Diseño e implementación de red subyacente de estructura IP

Para obtener una descripción general de los modelos y componentes subyacentes de estructura IP compatibles utilizados en estos diseños, consulte la sección Red subyacente de estructura ip en Componentes de arquitectura de modelo de estructura de centro de datos.

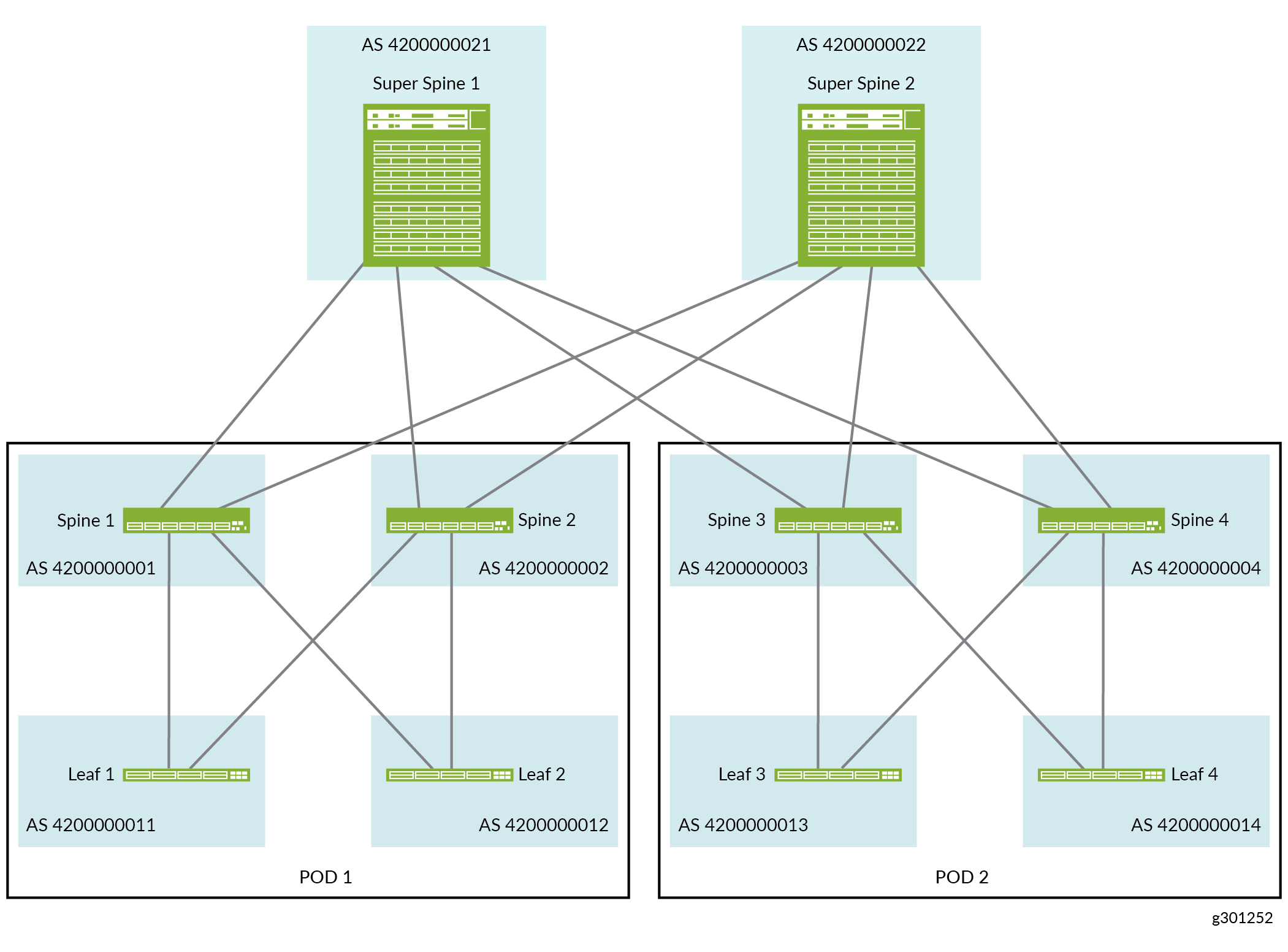

En esta sección, se explica cómo configurar dispositivos spine y leaf en capas subyacentes de estructura IPv4 de 3 y 5 etapas. Para obtener más información acerca de cómo configurar el nivel adicional de dispositivos super spine en una estructura ip subyacente de 5 etapas, consulte Diseño e implementación de estructura de IP de cinco etapas. Para obtener los pasos para configurar un diseño de estructura IPv6 en arquitecturas de referencia que admitan esa configuración, consulte Diseño e implementación de red con EBGP con capas subyacentes y superpuestas de estructura IPv6 .

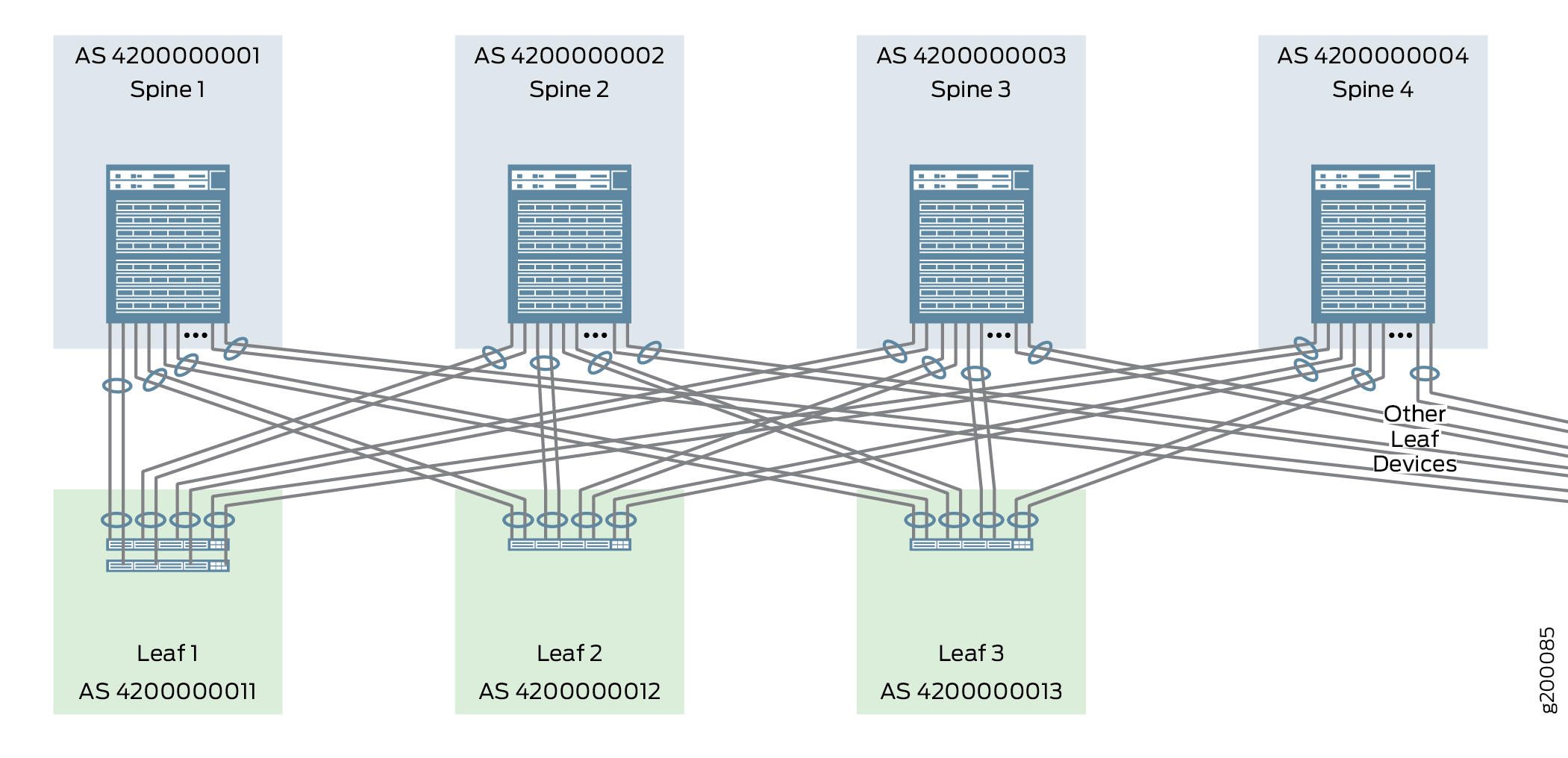

El bloque de construcción de red subyacente ip está organizado en una topología de estructura basada en Clos. La red subyacente usa EBGP como protocolo de enrutamiento en lugar de un IGP tradicional como OSPF. Puede usar otros protocolos de enrutamiento en el protocolo subyacente en su centro de datos; el uso de esos protocolos de enrutamiento está más allá del alcance de este documento.

Las interfaces Ethernet agregadas con MicroBFD también se utilizan en este bloque de construcción. MicroBFD mejora la detección de fallas en una interfaz Ethernet agregada mediante la ejecución de BFD en vínculos individuales de la interfaz Ethernet agregada.

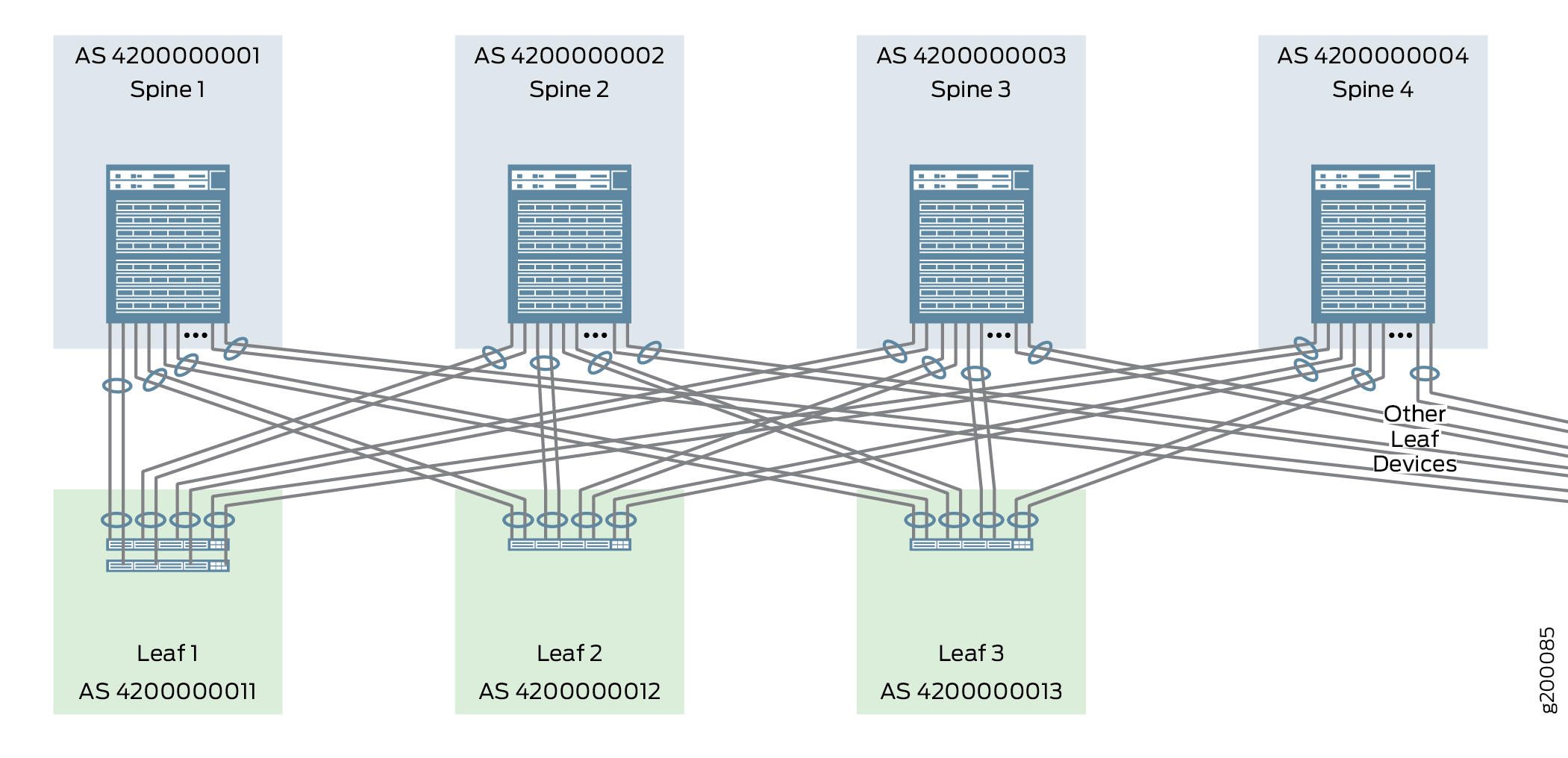

La Figura 1 y la Figura 2 proporcionan ilustraciones de alto nivel de redes subyacentes de estructura IP de 3 y 5 etapas, respectivamente.

Configuración de las interfaces Ethernet agregadas que conectan dispositivos spine a dispositivos leaf

En este diseño, cada dispositivo spine se interconecta con cada dispositivo leaf mediante un único vínculo o una interfaz Ethernet agregada de dos miembros. La decisión de usar un solo vínculo o una interfaz Ethernet agregada depende en gran medida de las necesidades de su red; consulte Descripción general del diseño de referencia de la estructura del centro de datos y topología validada para obtener más información sobre los requisitos de la interfaz.

La mayoría de las topologías de estructura IP no usan interfaces Ethernet agregadas para interconectar dispositivos spine y leaf. Puede omitir esta sección si está conectando sus dispositivos spine y leaf mediante vínculos únicos.

Utilice las siguientes instrucciones para configurar las interfaces que interconectan dispositivos spine y leaf como interfaces Ethernet agregadas con vínculos de dos miembros. Se asigna una dirección IPv4 a cada interfaz de Ethernet agregada. LaCP con un intervalo periódico rápido también está habilitado.

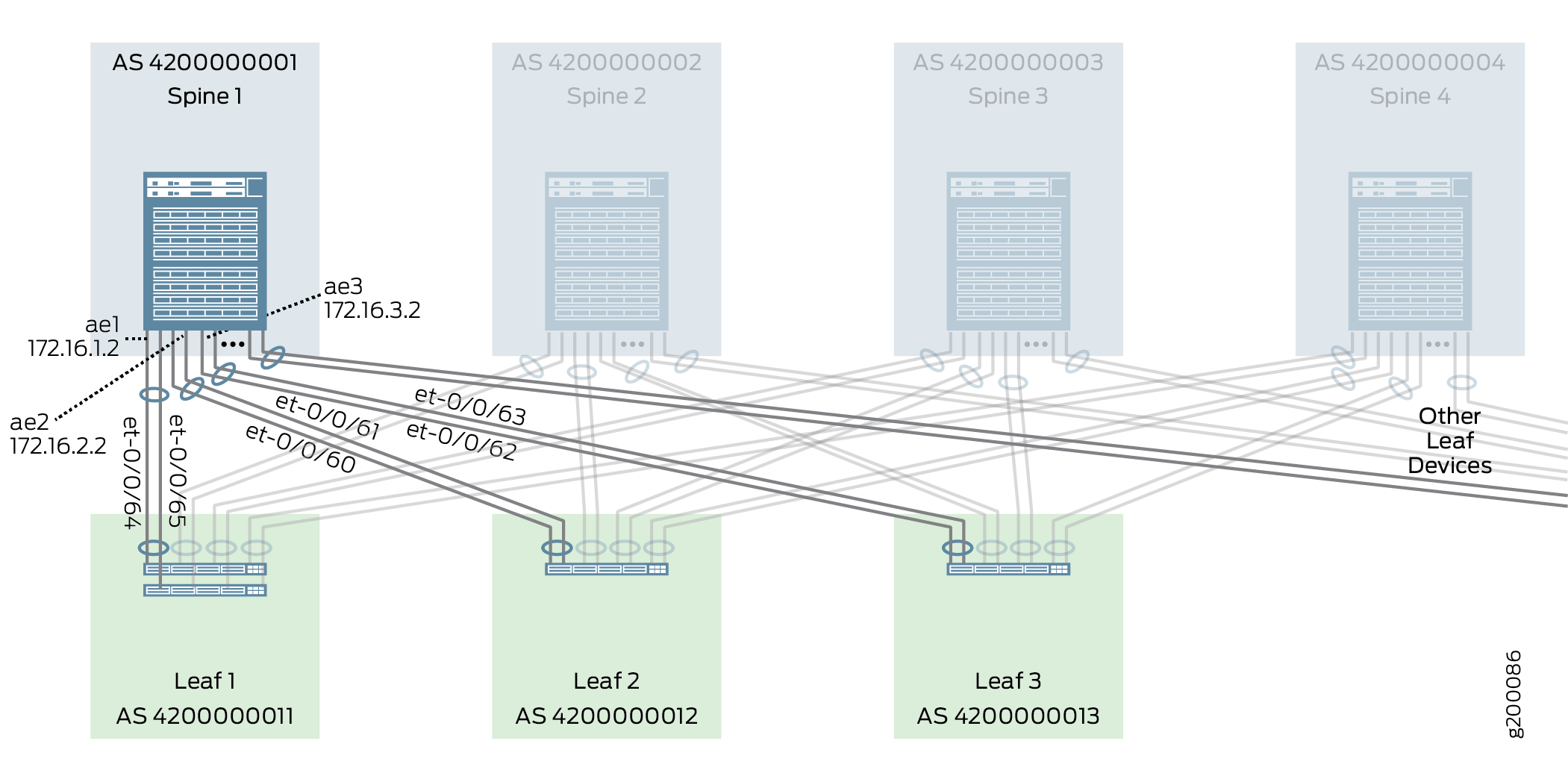

La Figura 3 muestra las interfaces de dispositivo spine que se configuran en este procedimiento:

spine 1

spine 1

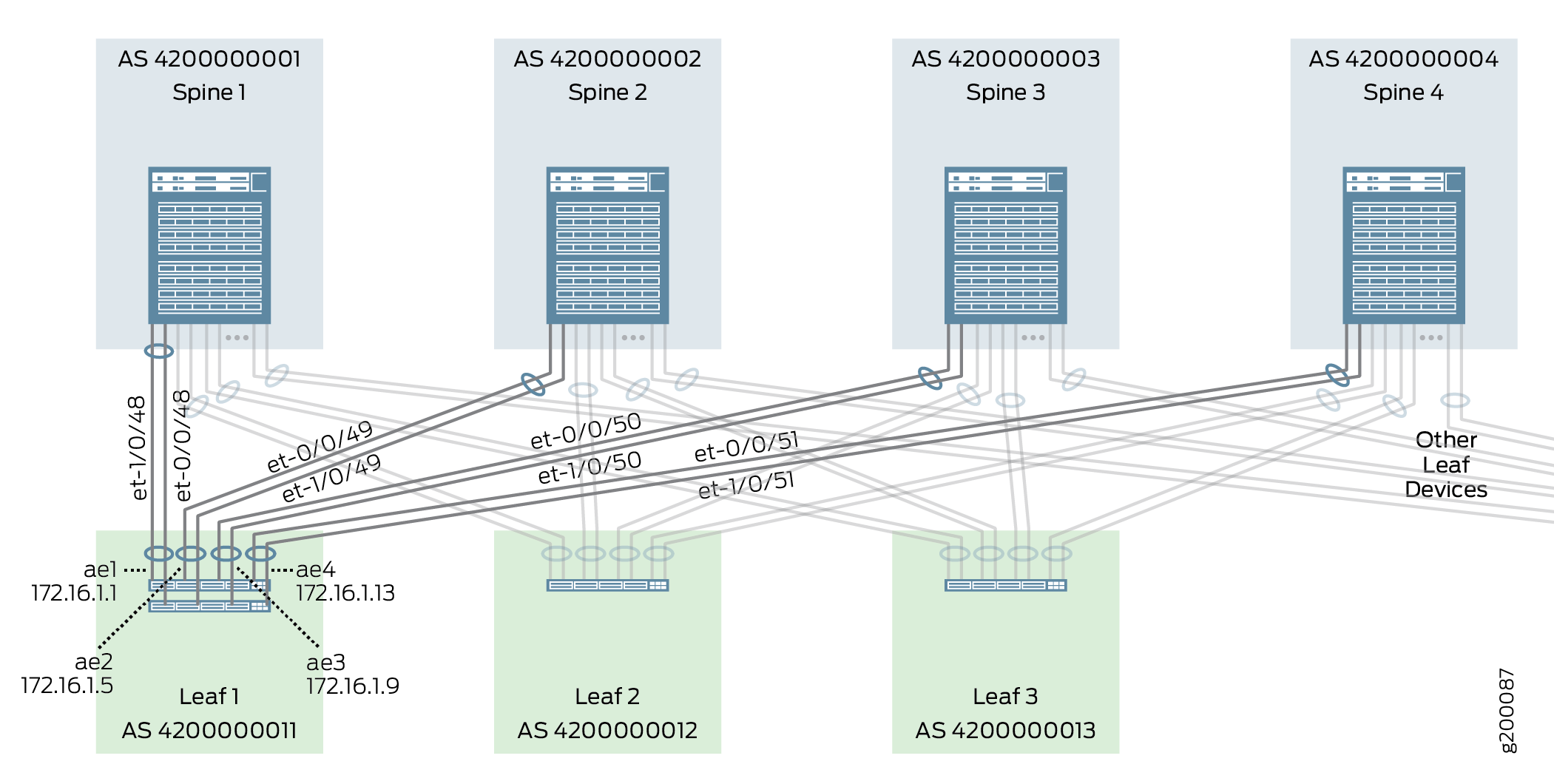

La Figura 4 muestra las interfaces de dispositivo leaf que se configuran en este procedimiento:

leaf 1

leaf 1

Para configurar interfaces Ethernet agregadas con LACP rápida:

Configurar una dirección IP para un vínculo individual

Esta sección cubre el procedimiento para agregar una dirección IP a una interfaz de vínculo único que conecta un dispositivo spine o leaf. El proceso para agregar una dirección IP a una interfaz Ethernet agregada se cubre en Configuración de las interfaces Ethernet agregadas que conectan dispositivos spine a dispositivos leaf.

Para agregar una dirección IP a una interfaz de vínculo único:

Habilitación del EBGP como protocolo de enrutamiento en la red subyacente

En este diseño, el EBGP es el protocolo de enrutamiento de la red subyacente y a cada dispositivo de la estructura IP se le asigna un número de sistema autónomo (ASN) único de 32 bits. La configuración del enrutamiento subyacente garantiza que todos los dispositivos de la estructura IP subyacente sean accesibles de manera confiable entre sí. La accesibilidad entre VTEP a través de la estructura IP subyacente también es necesaria para admitir redes superpuestas con VXLAN.

La Figura 5 muestra la configuración del EBGP de la red subyacente.

de la red subyacente del EBGP

de la red subyacente del EBGP

Para habilitar el EBGP como protocolo de enrutamiento para la red subyacente en un dispositivo:

Habilitación del equilibrio de carga

El equilibrio de carga de ECMP permite enviar tráfico al mismo destino a través de varias rutas de costo igual. Se debe habilitar el equilibrio de carga en todos los dispositivos spine y leaf para garantizar que el tráfico se envíe a través de todas las rutas disponibles proporcionadas por la estructura IP.

El tráfico está equilibrado de carga por flujo de capa 4 en dispositivos Junos. La carga del algoritmo ECMP equilibra cada flujo de tráfico en una de las múltiples rutas y todo el tráfico de ese flujo se transmite mediante el vínculo seleccionado.

Para habilitar el equilibrio de carga basado en ECMP en un dispositivo:

Configuración de la detección de reenvío micro bidireccional en vínculos miembros en interfaces Ethernet agregadas

BFD es un simple protocolo de detección de fallas bidireccional que verifica la conectividad bidireccional entre dispositivos conectados directamente mediante el envío periódico y rápido de un simple paquete de saludo a través del vínculo o vínculos que interconectan los dispositivos. El BFD puede detectar y comunicar fallas de vínculo en períodos de menos de dos segundos para permitir que el software del plano de control cambie rápidamente a una ruta alternativa.

MicroBFD permite que BFD se ejecute en vínculos de miembros individuales en una interfaz Ethernet agregada.

En este diseño, microBFD se admite en conexiones entre conmutadores QFX10002-36Q/72Q, QFX10008 y QFX10016.

Para habilitar la microBFD:

Red subyacente de estructura IP: historial de versiones

En la Tabla 1 se proporciona un historial de todas las características de esta sección y su soporte dentro de este diseño de referencia.

Lanzamiento |

Descripción |

|---|---|

19.1R2 |

Los conmutadores QFX10002-60C y QFX5120-32C que ejecutan la versión 19.1R2 de Junos OS y versiones posteriores en el mismo tren de versión también admiten todas las funciones documentadas en esta sección, excepto las siguientes:

|

18.4R2 |

Los conmutadores QFX5120-48Y que ejecutan Junos OS versión 18.4R2 y versiones posteriores en el mismo tren de versión admiten todas las funciones documentadas en esta sección, excepto MicroBFD. |

18.1R3-S3 |

Los conmutadores QFX5110 que ejecutan Junos OS versión 18.1R3-S3 y versiones posteriores en el mismo tren de versión admiten todas las funciones documentadas en esta sección, excepto MicroBFD. |

17.3R3-S1 |

Todos los dispositivos en el diseño de referencia que son compatibles con Junos OS versión 17.3R3-S1 y versiones posteriores en el mismo tren de versiones también admiten todas las funciones documentadas en esta sección. La siguiente es una excepción:

|