IP 패브릭 언더레이 네트워크 설계 및 구현

이러한 설계에서 사용되는 지원되는 IP 패브릭 언더레이 모델 및 구성 요소에 대한 개요는 데이터센터 패브릭 블루프린트 아키텍처 구성 요소의 IP 패브릭 언더레이 네트워크 섹션을 참조하십시오.

이 섹션에서는 3단계 및 5단계 IPv4 패브릭 언더레이에서 스파인 및 리프 디바이스를 구성하는 방법을 설명합니다. 5단계 IP 패브릭 언더레이에서 슈퍼 스파인 디바이스의 추가 계층을 구성하는 방법에 대한 자세한 내용은 5단계 IP 패브릭 설계 및 구현을 참조하십시오. 이러한 구성을 지원하는 참조 아키텍처에서 IPv6 패브릭 설계를 구성하는 단계는 대신 EBGP를 통한 IPv6 패브릭 언더레이 및 오버레이 네트워크 설계 및 구현을 참조하십시오.

IP 언더레이 네트워크 빌딩 블록은 Clos 기반 패브릭 토폴로지로 배열됩니다. 언더레이 네트워크는 OSPF와 같은 기존 IGP 대신 EBGP를 라우팅 프로토콜로 사용합니다. 데이터센터의 언더레이 프로토콜에서 다른 라우팅 프로토콜을 사용할 수 있습니다. 이러한 라우팅 프로토콜의 사용은 이 문서의 범위를 벗어나 있습니다.

이 빌딩 블록에도 마이크로BFD가 있는 어그리게이션 이더넷 인터페이스가 사용됩니다. MicroBFD는 어그리게이션 이더넷 인터페이스의 개별 링크에서 BFD를 실행하여 어그리게이션 이더넷 인터페이스에서 결함 탐지를 개선합니다.

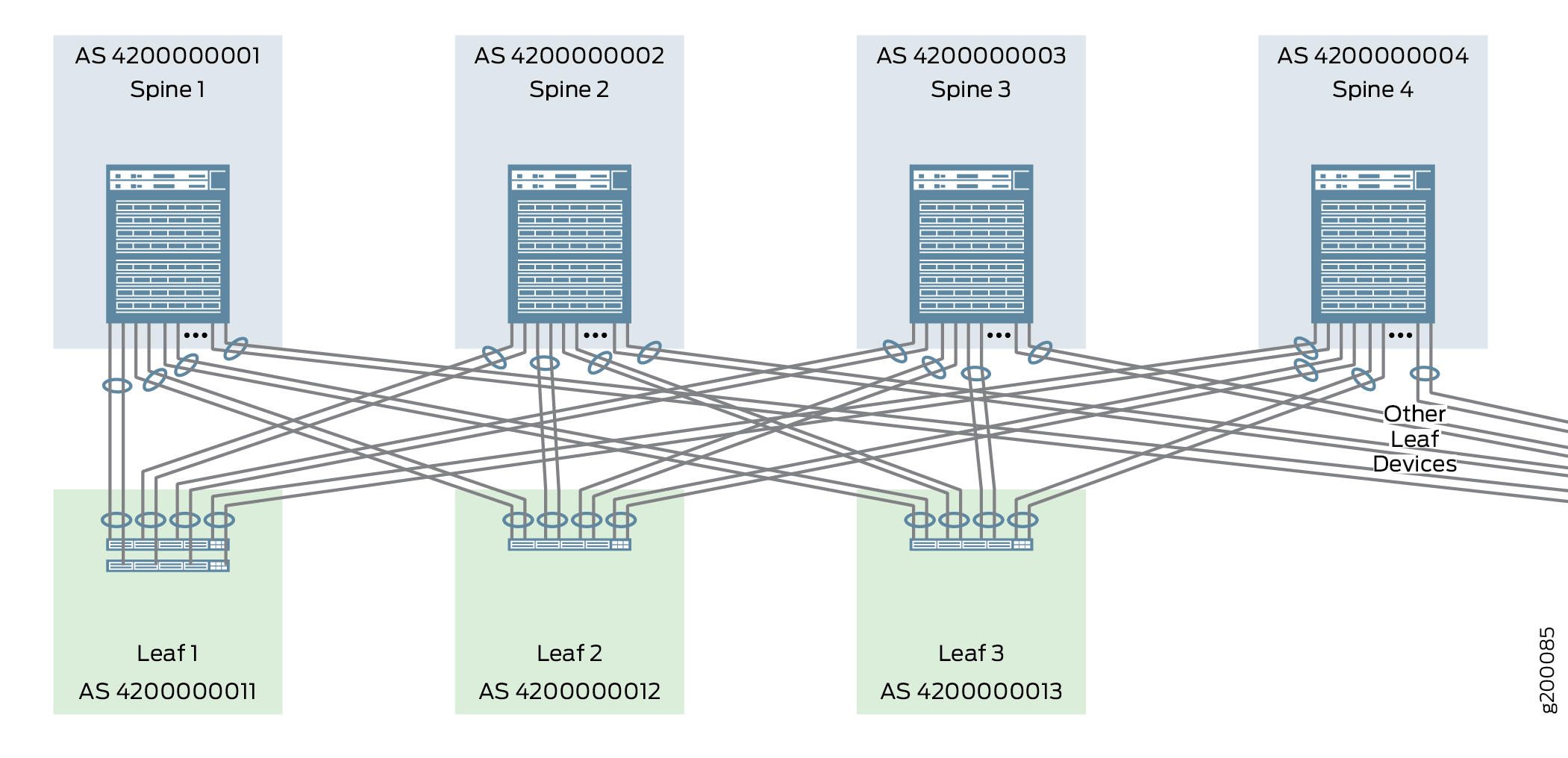

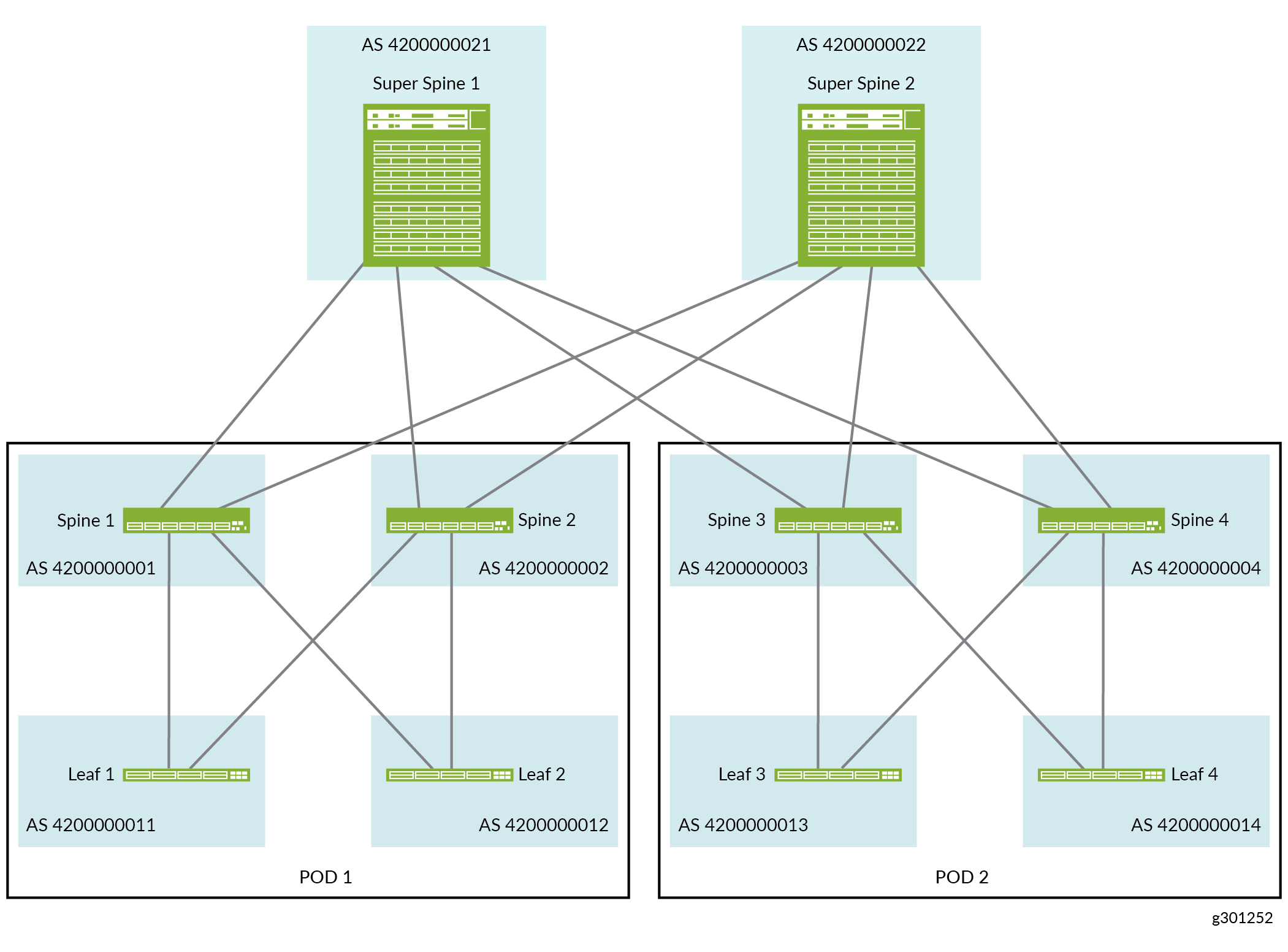

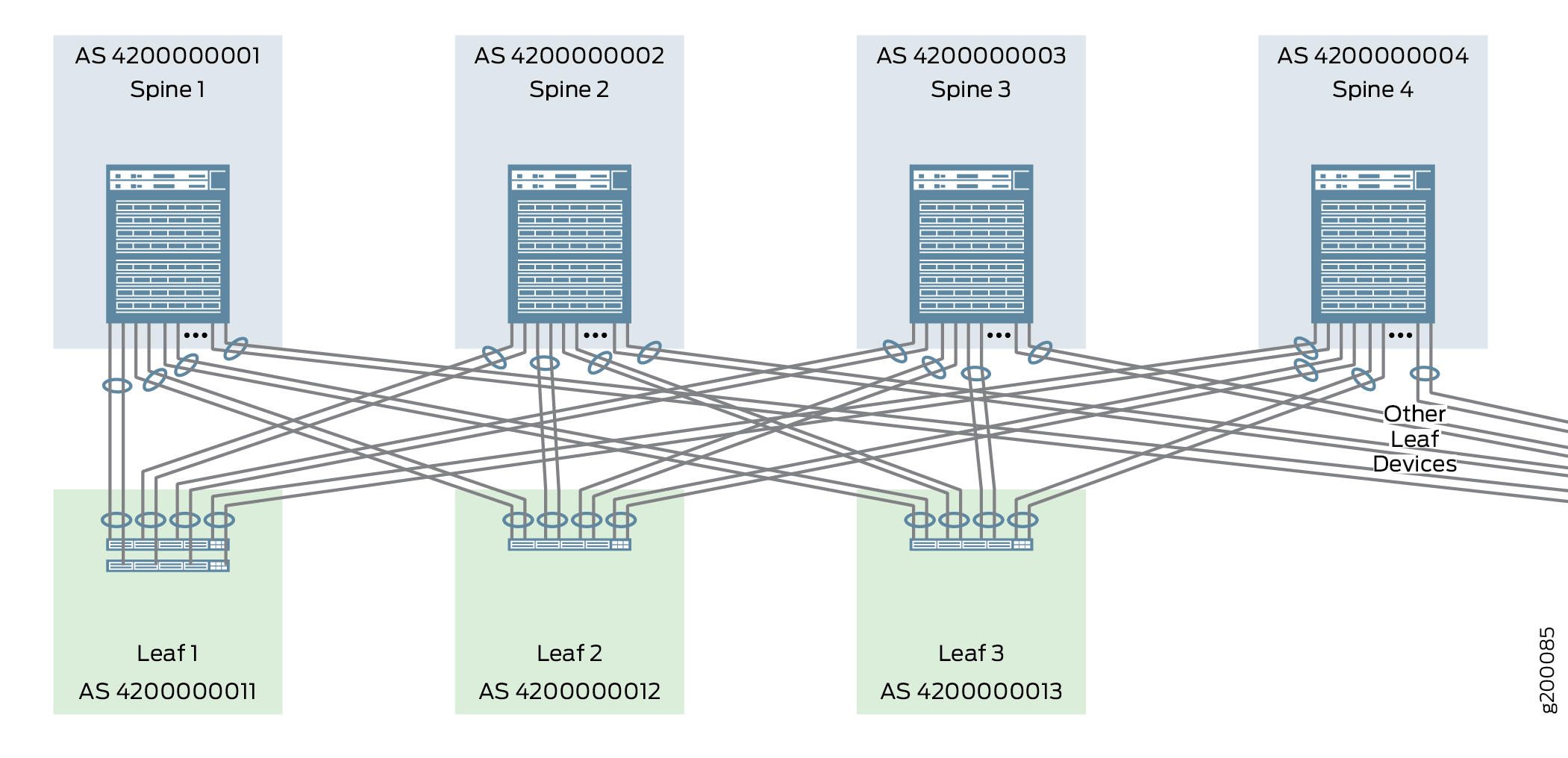

그림 1 과 그림 2 는 각각 3단계 및 5단계 IP 패브릭 언더레이 네트워크에 대한 높은 수준의 그림을 제공합니다.

스파인 디바이스를 리프 디바이스에 연결하는 어그리게이션 이더넷 인터페이스 구성

이 설계에서 각 스파인 디바이스 단일 링크 또는 2개의 멤버 어그리게이션 이더넷 인터페이스를 사용하여 각 리프 디바이스에 상호 연결됩니다. 단일 링크 또는 어그리게이션 이더넷 인터페이스를 사용하기로 결정하는 것은 주로 네트워크의 요구 사항에 따라 달라집니다. 인터페이스 요구 사항에 대한 자세한 내용은 데이터센터 패브릭 참조 설계 개요 및 검증된 토폴로지 에서 확인하십시오.

대부분의 IP 패브릭 토폴로지에서는 어그리게이션 이더넷 인터페이스를 사용하여 스파인 및 리프 디바이스를 상호 연결하지 않습니다. 단일 링크를 사용하여 스파인 및 리프 디바이스를 연결하는 경우 이 섹션을 건너뛰게 됩니다.

다음 지침을 사용하여 스파인 및 리프 디바이스를 두 개의 멤버 링크가 있는 어그리게이션 이더넷 인터페이스로 상호 연결하는 인터페이스를 구성합니다. IPv4 주소는 각 어그리게이션 이더넷 인터페이스에 할당됩니다. 빠른 주기 간격을 가진 LACP도 활성화됩니다.

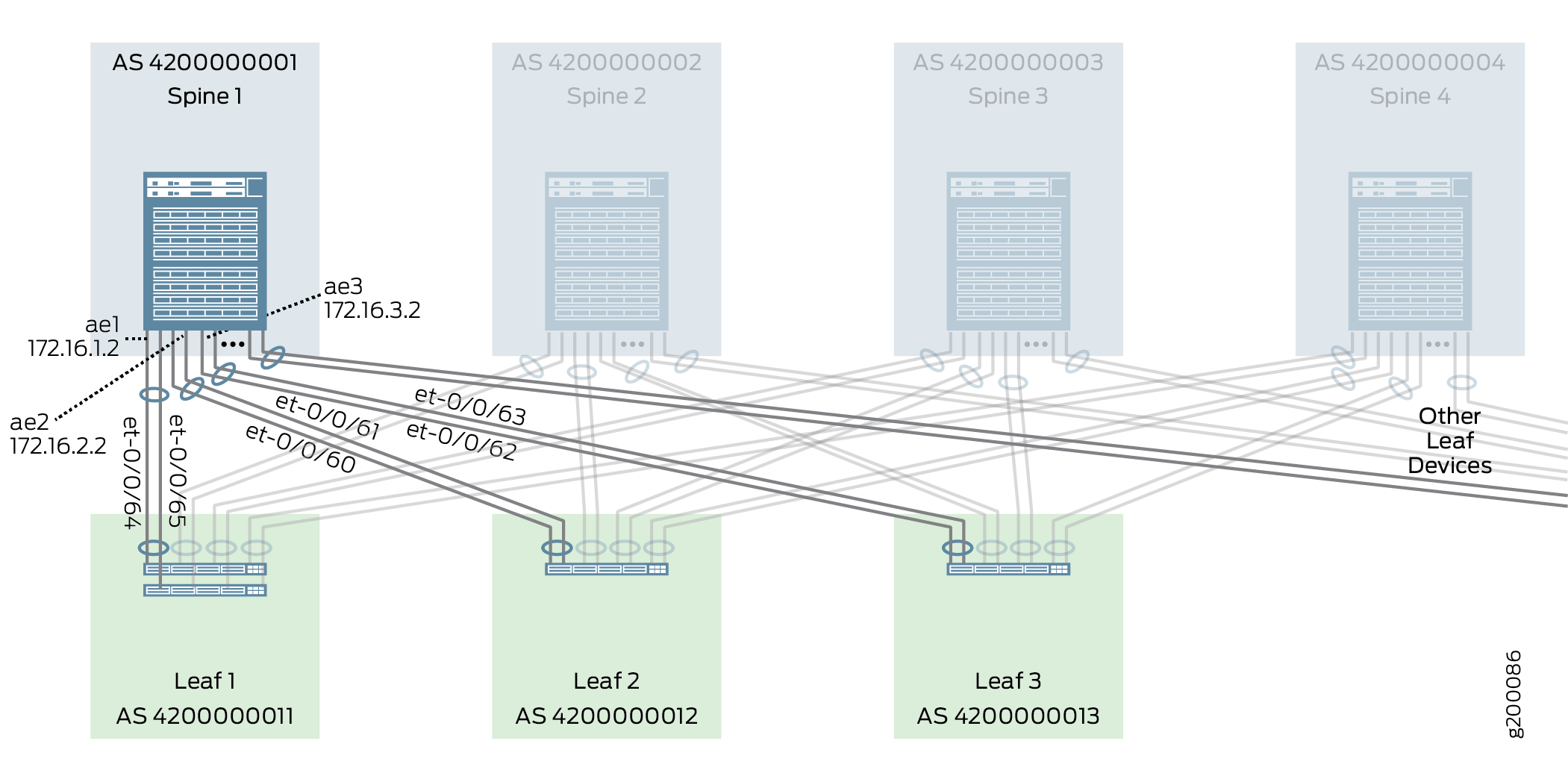

그림 3 은 이 절차에서 구성된 스파인 디바이스 인터페이스를 보여줍니다.

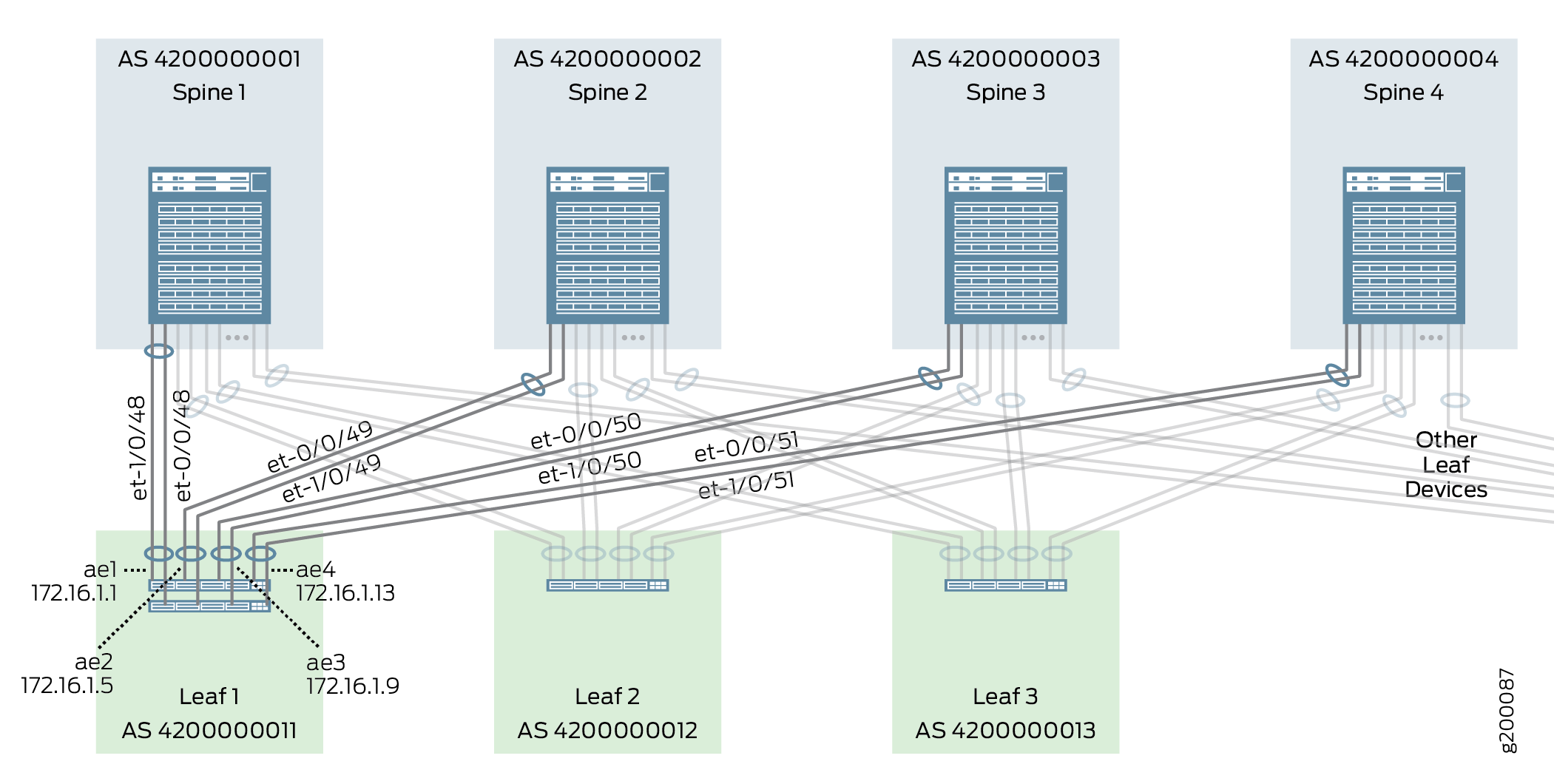

그림 4 는 이 절차에서 구성된 리프 디바이스 인터페이스를 보여줍니다.

빠른 LACP로 어그리게이션 이더넷 인터페이스 구성 방법:

개별 링크에 대한 IP 주소 구성

이 섹션에서는 스파인 또는 리프 디바이스를 연결하는 단일 링크 인터페이스에 IP 주소를 추가하는 절차를 다룹니다. 어그리게이션 이더넷 인터페이스에 IP 주소를 추가하는 프로세스는 스파인 디바이스를 리프 디바이스에 연결하는 어그리게이션 이더넷 인터페이스 구성에서 다룹니다.

단일 링크 인터페이스에 IP 주소를 추가하려면 다음을 수행합니다.

언더레이 네트워크에서 라우팅 프로토콜로 EBGP 활성화

이 설계에서 EBGP는 언더레이 네트워크의 라우팅 프로토콜이며 IP 패브릭의 각 디바이스에는 고유한 32비트 ASN(Autonomous System Number)이 할당됩니다. 언더레이 라우팅 구성은 언더레이 IP 패브릭의 모든 디바이스가 서로 안정적으로 연결할 수 있도록 합니다. 또한 VXLAN을 통한 오버레이 네트워킹을 지원하려면 언더레이 IP 패브릭 전반에서 VTEP 간 도달 가능성이 필요합니다.

그림 5 는 언더레이 네트워크의 EBGP 구성을 보여줍니다.

디바이스에서 언더레이 네트워크에 대한 라우팅 프로토콜로 EBGP를 활성화하려면,

로드 밸런싱 활성화

ECMP 로드 밸런싱을 사용하면 여러 동일한 비용 경로를 통해 동일한 대상으로 트래픽을 전송할 수 있습니다. IP 패브릭에서 제공하는 사용 가능한 모든 경로를 통해 트래픽이 전송되도록 하려면 모든 스파인 및 리프 디바이스에서 로드 밸런싱을 활성화해야 합니다.

Junos 디바이스의 레이어 4 플로우에 따라 트래픽 로드 밸런서가 표시됩니다. ECMP 알고리즘은 여러 경로 중 하나를 통해 각 트래픽 플로우를 로드 밸런시하며, 해당 플로우에 대한 모든 트래픽은 선택한 링크를 사용하여 전송됩니다.

디바이스에서 ECMP 기반 로드 밸런싱을 활성화하려면,

어그리게이션 이더넷 인터페이스의 멤버 링크에서 마이크로 양방향 포워딩 탐지 구성

BFD는 디바이스를 상호 연결하는 링크 또는 링크를 통해 주기적으로 신속하게 간단한 Hello 패킷을 전송하여 직접 연결된 디바이스 간의 양방향 연결을 검증하는 간단한 양방향 결함 탐지 프로토콜입니다. BFD는 컨트롤 플레인 소프트웨어가 신속하게 대체 경로로 전환할 수 있도록 1초 미만의 시간 프레임에서 링크 결함을 감지하고 통신할 수 있습니다.

마이크로 BFD는 BFD가 어그리게이션 이더넷 인터페이스의 개별 멤버 링크에서 실행되도록 허용합니다.

이 설계에서 마이크로BFD는 QFX10002-36Q/72Q, QFX10008 및 QFX10016 스위치 간의 연결에서 지원됩니다.

마이크로 BFD를 활성화하려면:

IP 패브릭 언더레이 네트워크 — 릴리스 기록

표 1 은 이 섹션에 있는 모든 기능과 이 참조 설계 내의 해당 기능에 대한 기록을 제공합니다.

릴리스 |

설명 |

|---|---|

19.1R2 |

동일한 릴리스 트레인에서 Junos OS 릴리스 19.1R2 이상 릴리스를 실행하는 QFX10002-60C 및 QFX5120-32C 스위치는 다음을 제외하고 이 섹션에 문서화된 모든 기능을 지원합니다.

|

18.4R2 |

릴리스 18.4R2 및 이후 버전에서 Junos OS 실행되는 QFX5120-48Y 스위치는 MicroBFD를 제외한 이 섹션에 문서화된 모든 기능을 지원합니다. |

18.1R3-S3 |

릴리스 18.1R3-S3 및 이후 버전에서 Junos OS 실행되는 QFX5110 스위치는 MicroBFD를 제외한 이 섹션에 문서화된 모든 기능을 지원합니다. |

17.3R3-S1 |

동일한 릴리스 트레인에서 릴리스 17.3R3-S1 및 이후 릴리스를 지원하는 Junos OS 레퍼런스 설계의 모든 디바이스도 이 섹션에 문서화된 모든 기능을 지원합니다. 다음은 예외입니다.

|