IPファブリックアンダーレイネットワークの設計と実装

これらの設計で使用されるサポートされているIPファブリックアンダーレイモデルとコンポーネントの概要については、データセンターファブリックブループリントアーキテクチャコンポーネントのIPファブリックアンダーレイネットワークセクションを参照してください。

このセクションでは、3ステージおよび5ステージのIPv4ファブリックアンダーレイでスパイン/リーフデバイスを設定する方法について説明します。5ステージIPファブリックアンダーレイでスーパースパインデバイスの追加階層を設定する方法については、 5 ステージIPファブリックの設計と実装を参照してください。その設定をサポートするリファレンスアーキテクチャでIPv6ファブリック設計を設定する手順については、代わりにEBGPを使用した IPv6ファブリックアンダーレイとオーバーレイネットワーク設計と実装 を参照してください。

IP アンダーレイ ネットワークの構成要素は、Clos ベースのファブリック トポロジーに配置されています。アンダーレイネットワークは、OSPFのような従来のIGPの代わりに、EBGPをルーティングプロトコルとして使用します。データセンターのアンダーレイプロトコルで他のルーティングプロトコルを使用できます。これらのルーティングプロトコルの使用は、本書の範囲外です。

この構成要素には、MicroBFDを使用した集合型イーサネット・インタフェースも使用されています。マイクロBFDは、集合型イーサネット・インタフェースの個々のリンクでBFDを実行することで、集合型イーサネット・インタフェースの障害検出を改善します。

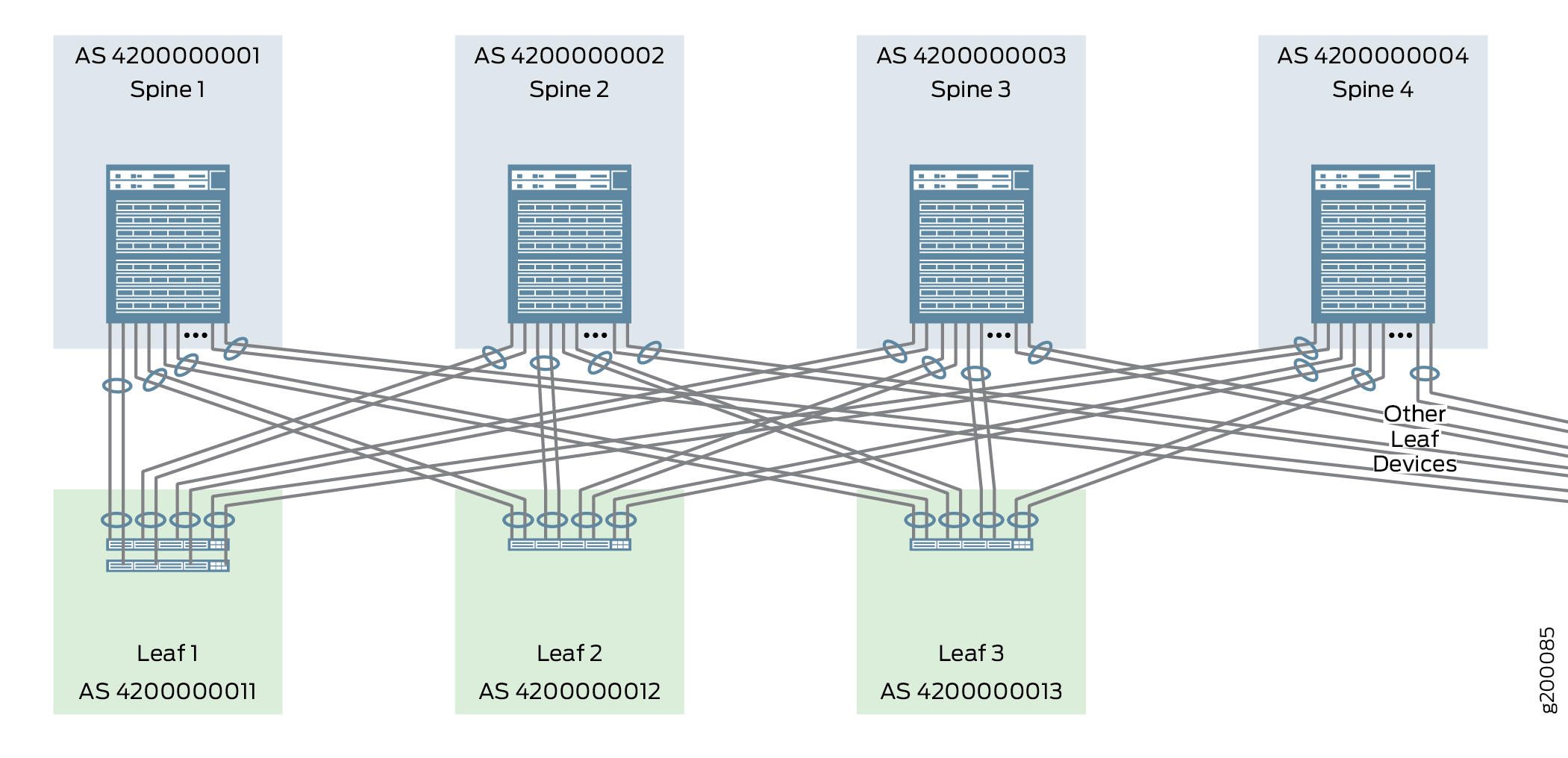

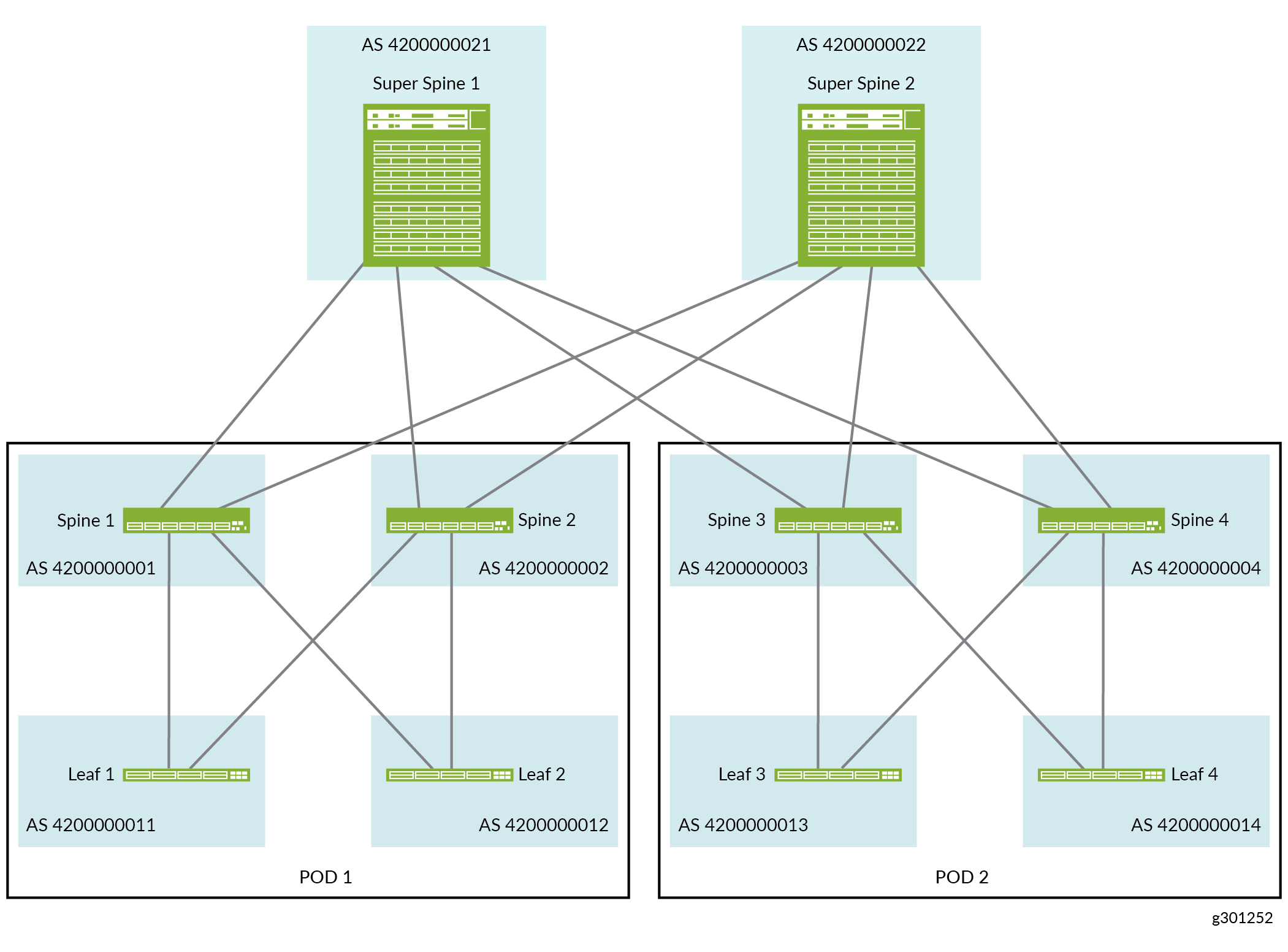

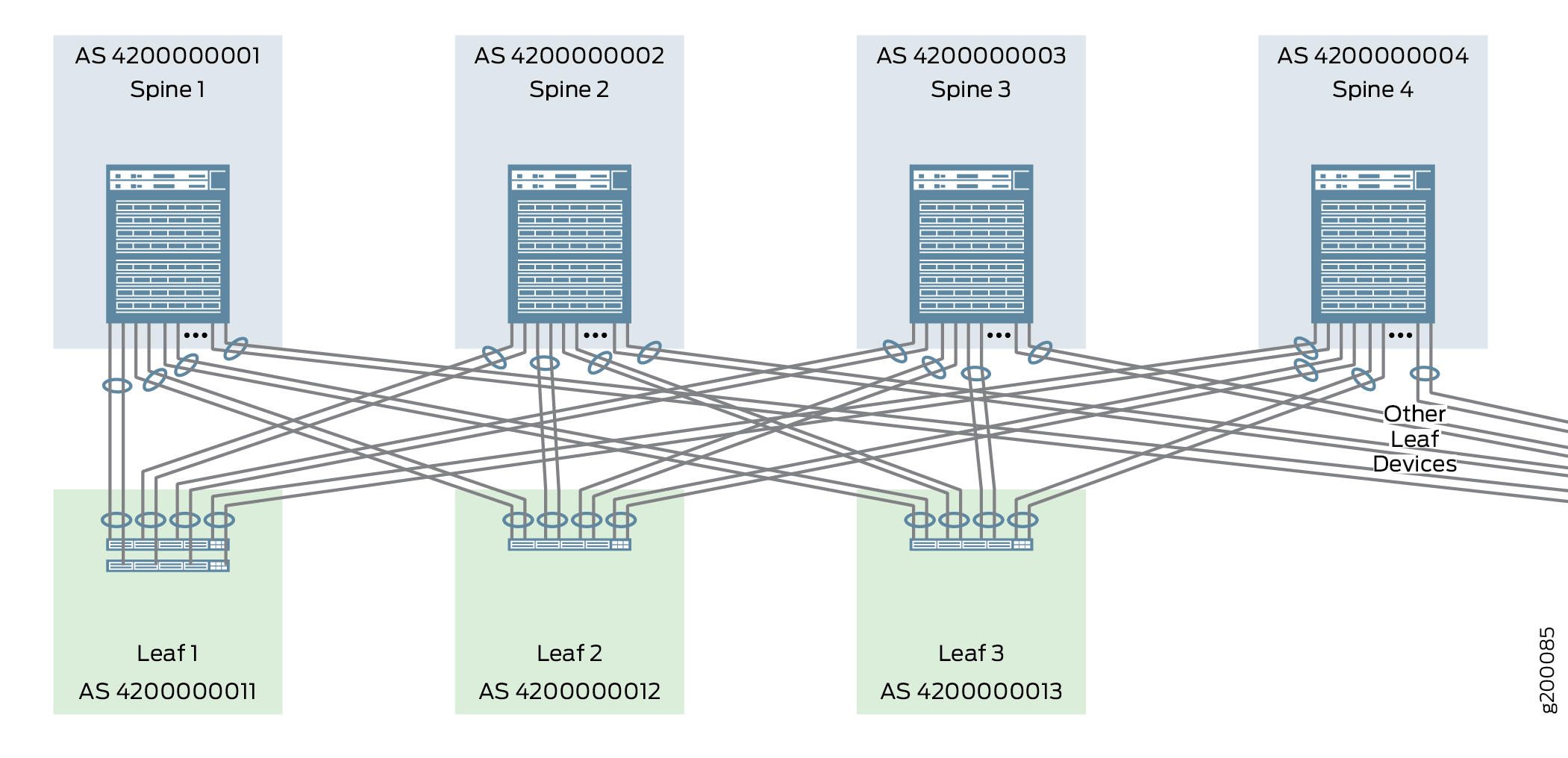

図 1 と 図 2 に、それぞれ 3 ステージと 5 ステージの IP ファブリック アンダーレイ ネットワークの概要図を示します。

スパインデバイスとリーフデバイスを接続する集合型イーサネットインターフェイスの設定

この設計では、各スパインデバイスは、単一のリンクまたは2メンバーの集合型イーサネットインターフェイスを使用して、各リーフデバイスに相互接続されています。単一リンクまたは集合型イーサネット・インターフェースの使用は、ネットワークのニーズによって大きく異なります。インターフェイス要件の詳細については、 データセンターファブリックリファレンス設計の概要と検証済みトポロジー を参照してください。

IPファブリックトポロジーの大部分は、スパインデバイスとリーフデバイスを相互接続するために集合型イーサネットインターフェイスを使用していません。単一リンクを使用してスパインデバイスとリーフデバイスを接続する場合は、このセクションをスキップできます。

スパインおよびリーフデバイスを相互接続するインターフェイスを、2つのメンバーリンクを持つ集合型イーサネットインターフェイスとして設定するには、次の手順に従います。IPv4アドレスは、各集合型イーサネットインターフェイスに割り当てられます。高速の定期的な間隔を持つ LACP も有効です。

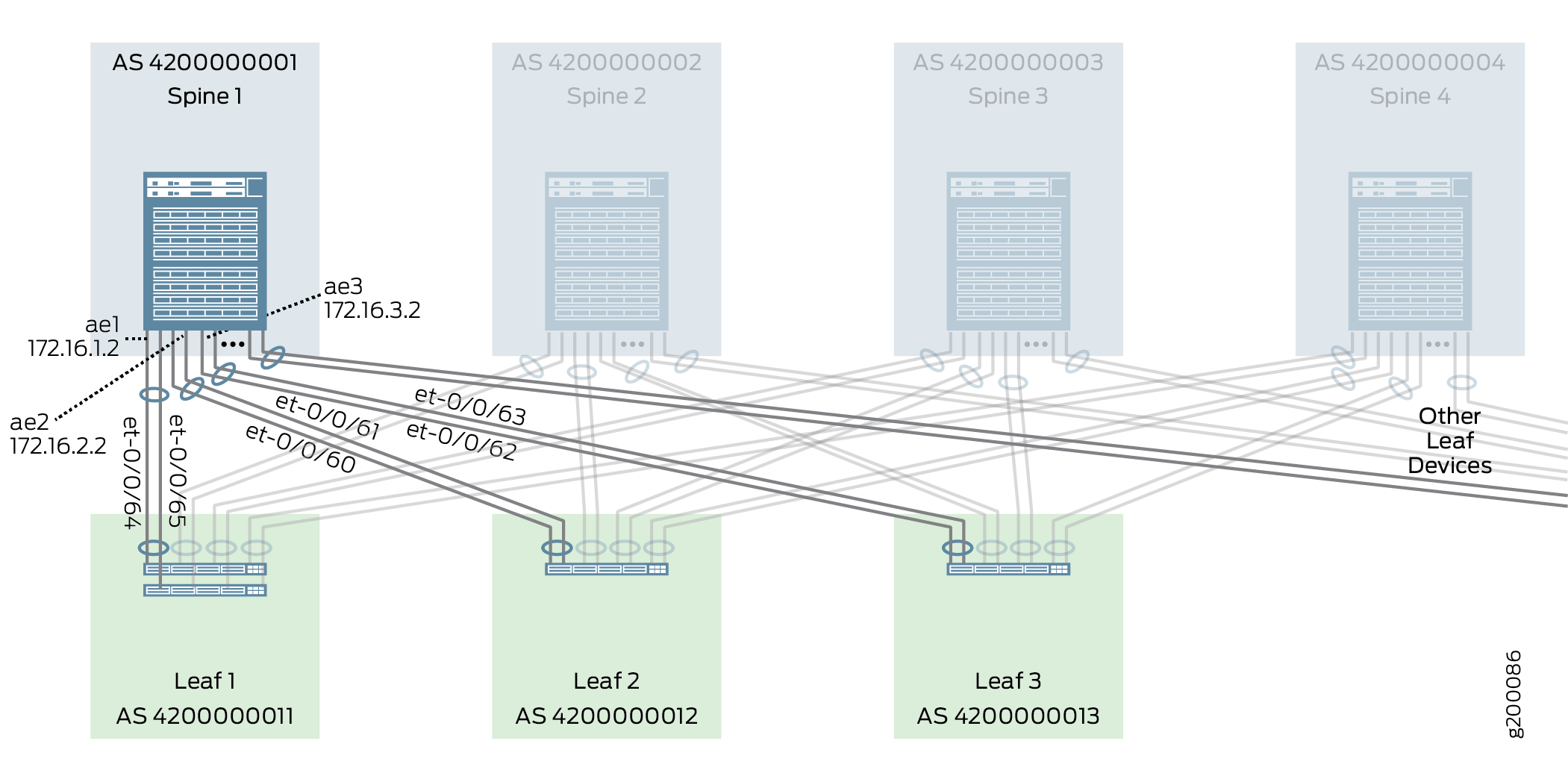

図 3 は、この手順で設定されたスパイン デバイス インターフェイスを示しています。

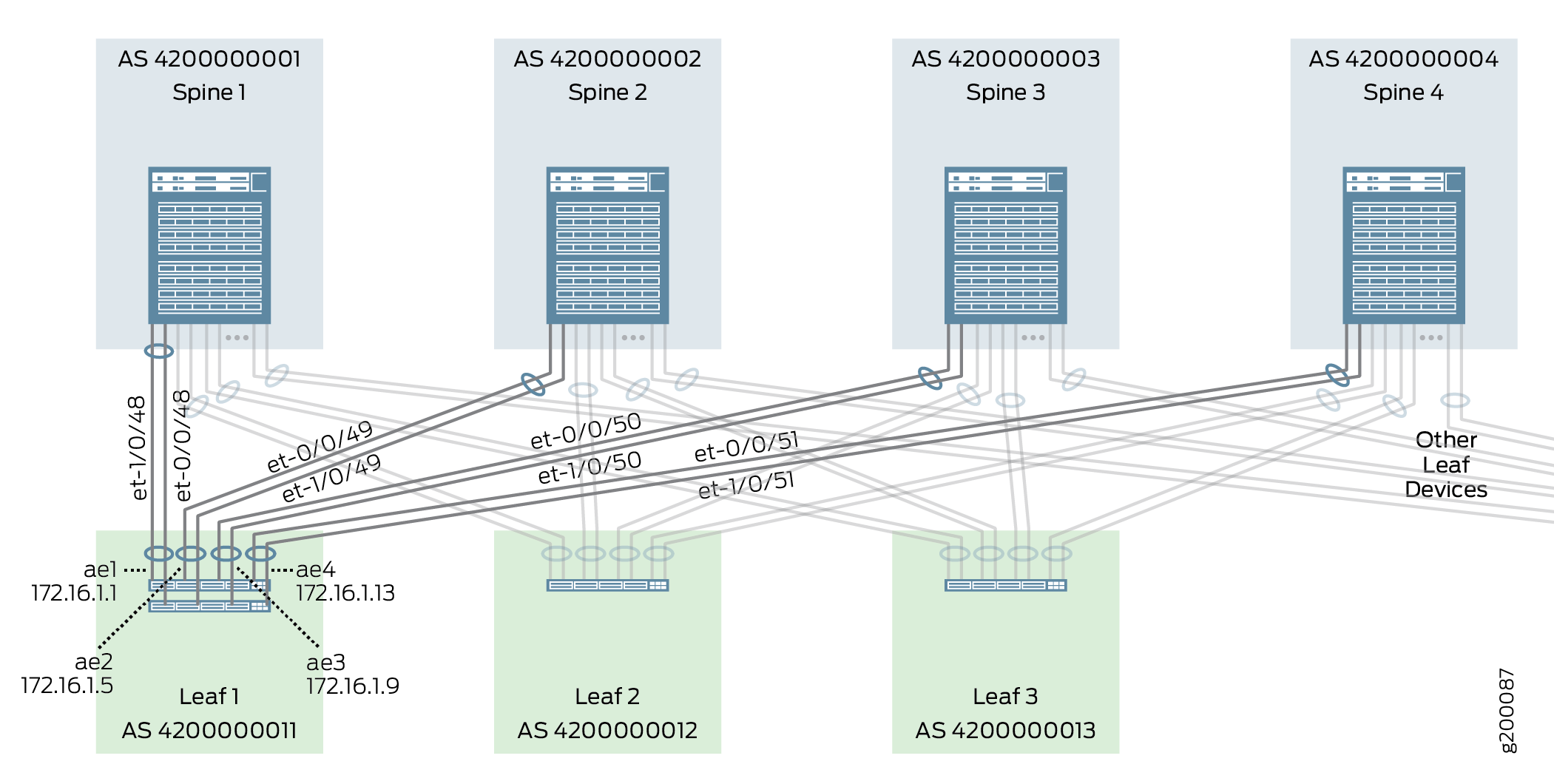

図4 は、この手順で設定されたリーフデバイスインターフェイスを示しています。

高速LACPで集合型イーサネット・インタフェースを設定するには:

個々のリンクにIPアドレスを設定する

このセクションでは、スパインまたはリーフデバイスを接続する単一のリンクインターフェイスにIPアドレスを追加する手順について説明します。集合型イーサネットインターフェイスにIPアドレスを追加するプロセスについては、 スパインデバイスをリーフデバイスに接続するアグリゲートイーサネットインターフェイスの設定を参照してください。

単一のリンク インターフェイスに IP アドレスを追加するには、次の手順に従います。

アンダーレイ ネットワークで EBGP をルーティング プロトコルとして有効化

この設計では、EBGP はアンダーレイ ネットワークのルーティング プロトコルであり、IP ファブリック内の各デバイスには固有の 32 ビット自律システム番号(ASN)が割り当てられます。アンダーレイルーティング構成により、アンダーレイIPファブリック内のすべてのデバイスが確実に互いに到達可能になります。VXLANを使用したオーバーレイネットワークをサポートするには、アンダーレイIPファブリック間のVTEP間の到達可能性も必要です。

図 5 は、アンダーレイ ネットワークの EBGP 設定を示しています。

デバイス上のアンダーレイネットワークのルーティングプロトコルとしてEBGPを有効にするには:

ロードバランシングの有効化

ECMP ロード バランシングにより、複数の等コスト パスを介して同じ宛先にトラフィックを送信できます。IPファブリックが提供するすべての利用可能なパスを介してトラフィックを確実に送信するためには、すべてのスパインおよびリーフデバイスでロードバランシングを有効にする必要があります。

Junos デバイス上のレイヤー 4 フローごとにトラフィックが負荷分散されます。ECMP アルゴリズムは、複数のパスの 1 つを介して各トラフィック フローを負荷分散し、そのフローのすべてのトラフィックが選択したリンクを使用して送信されます。

デバイスでECMPベースのロードバランシングを有効にするには:

集合型イーサネット・インターフェースのメンバー・リンクでのマイクロ双方向転送検出の設定

BFDは、直接接続されたデバイス間の双方向接続を検証するシンプルな双方向障害検出プロトコルで、デバイスを相互接続するリンクまたはリンクを介して簡単なhelloパケットを定期的かつ迅速に送信します。BFDは、1秒以下のタイムフレーム内のリンク障害を検出して通信することで、コントロールプレーンソフトウェアが代替パスに素早く切り替えることができます。

マイクロBFDにより、集合型イーサネット・インタフェース内の個々のメンバー・リンク上でBFDを実行することができます。

この設計では、QFX10002-36Q/72Q、QFX10008、QFX10016スイッチ間の接続でマイクロBFDがサポートされています。

マイクロBFDを有効にするには:

IP ファブリック アンダーレイ ネットワーク — リリース履歴

表 1 は、このセクションのすべての機能の履歴と、このリファレンス デザインでのサポートを示しています。

リリース |

説明 |

|---|---|

19.1R2 |

同じリリーストレインでJunos OSリリース19.1R2以降のリリースを実行しているQFX10002-60CおよびQFX5120-32Cスイッチは、以下を除くこのセクションで記載されているすべての機能もサポートしています。

|

18.4R2 |

同じリリーストレインでJunos OSリリース18.4R2以降のリリースを実行しているQFX5120-48Yスイッチは、マイクロBFDを除くこのセクションで記載されているすべての機能をサポートしています。 |

18.1R3-S3 |

同じリリーストレインでJunos OSリリース18.1R3-S3以降のリリースを実行しているQFX5110スイッチは、MicroBFDを除くこのセクションで記載されているすべての機能をサポートしています。 |

17.3R3-S1 |

同じリリーストレインでJunos OSリリース17.3R3-S1以降のリリースをサポートするリファレンスデザインのすべてのデバイスは、このセクションで記載されているすべての機能もサポートしています。以下は例外です。

|