Descripción general del software de diagnóstico del acelerador de flujo de paquetes y otras utilidades

Puede utilizar el software de diagnóstico del acelerador de flujo de paquetes para validar la integridad del módulo QFX-PFA-4Q y del conmutador QFX5100-24Q-AA. El software de diagnóstico del acelerador de flujo de paquetes contiene diagnósticos estándar, diagnósticos de orquestación, protocolo de tiempo de precisión (PTP) y diagnósticos de sincronización, y otras utilidades. El software de diagnóstico del acelerador de flujo de paquetes se ejecuta en una máquina virtual (VM) invitada en el conmutador QFX5100-24Q-AA y requiere que configure las opciones de la máquina virtual invitada en la CLI de Junos OS.

El módulo QFX-PFA-4Q contiene cuatro interfaces QSFP+ de 40 Gigabit Ethernet, un módulo FPGA e interfaces de entrada y salida de temporización para admitir aplicaciones de Protocolo de tiempo de precisión. El módulo FPGA contiene lógica que puede personalizar para procesar transacciones de alto volumen y con un uso intensivo de la latencia.

Antes de poder ejecutar el software y las utilidades de Packet Flow Accelerator Diagnostics, asegúrese de haber realizado las siguientes tareas:

Verifique que haya instalado el módulo QFX-PFA-4Q instalado en el conmutador QFX5100-24Q-AA. Para obtener más información, consulte Instalación de un módulo de expansión en un dispositivo QFX5100

Asegúrese de tener instalado Junos OS versión 14.1X53-D27 con automatización mejorada en el conmutador QFX5100-24Q-AA. Para obtener más información, consulte Instalación de paquetes de software en dispositivos de la serie QFX.

Instale el software Packet Flow Accelerator Diagnostics. Para obtener más información, consulte ../topic-map/packet-flow-accelerator-diagnostics-software.html#id-installing-packet-flow-accelerator-diagnostics-software.

Puertos externos e internos y puertos de tarjeta de interfaz de red

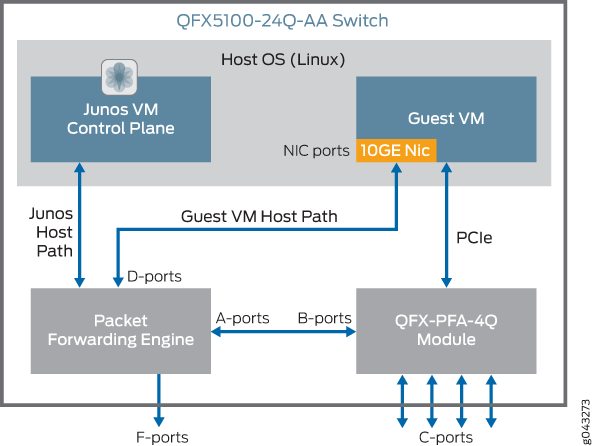

El software y las utilidades de Packet Flow Accelerator Diagnostics validan las rutas de datos entre los puertos externo e interno en el conmutador QFX5100-24Q-AA y el módulo QFX-PFA-4Q. Figura 1 ilustra los nombres de los puertos del conmutador QFX5100-24Q-AA y del módulo QFX-PFA-4Q y cómo se conectan.

Tabla 1 proporciona información sobre los puertos externos e internos, así como sobre los puertos NIC del conmutador QFX5100-24Q-AA y del módulo QFX-PFA-4Q.

Puertos A |

Las interfaces xe-0/0/24 a xe-0/0/39 en el motor de reenvío de paquetes (PFE) del conmutador QFX5100-24Q-AA se conectan a los puertos B del módulo FPGA del módulo de expansión QFX-PFA-4Q. Los puertos A requieren los puertos B correspondientes en el módulo FPGA. Puede administrar estas interfaces a través de Junos OS. |

Puertos B |

Los puertos internos de 10 Gigabit Ethernet se conectan al módulo FPGA del módulo QFX-PFA-4Q, que luego se conecta a los puertos A del PFE del conmutador QFX5100-24Q-AA. La convención de nomenclatura para estos puertos viene determinada por la máquina virtual invitada. La máquina virtual invitada controla el módulo FPGA. |

Puertos C |

Cuatro puertos frontales de 40 Gigabit Ethernet del módulo QFX-PFA-4Q se conectan al módulo FPGA que se ejecuta en el conmutador QFX5100-24Q-AA y a los puertos F del conmutador QFX5100-24Q-AA. La máquina virtual invitada controla el módulo FPGA. |

Puertos D |

Dos puertos internos Ethernet de 10 Gigabit en el motor de reenvío de paquetes del conmutador QFX5100-24Q-AA se conectan a la NIC Ethernet en el conmutador QFX5100-24Q-AA. La convención de nomenclatura para estos puertos es la misma que se utiliza para los puertos F. Puede administrar estos puertos a través de Junos OS. |

Puertos F |

Veinticuatro puertos frontales de 40 Gigabit Ethernet en el conmutador QFX5100-24Q-AA. Estos puertos contienen un prefijo "et" cuando están en modo 40 Gigabit Ethernet. Si canaliza estas interfaces, el prefijo es "xe". Puede administrar estos puertos a través de Junos OS. |

Puertos NIC |

Las interfaces internas xe-0/0/40 y xe-0/0/41 en el conmutador QFX5100-24Q-AA se conectan al PFE para su uso en la máquina virtual invitada. Los puertos NIC realizan las mismas funciones que cualquier otro puerto NIC del sistema operativo Linux. Los puertos NIC no funcionan a menos que esté instalado el módulo QFX-PFA-4Q. |

Acelerador de flujo de paquetes Pruebas y scripts de software de diagnóstico

Puede ejecutar el software de diagnóstico del acelerador de flujo de paquetes para probar los siguientes subsistemas en el módulo QFX-PFA-4Q:

FPGA

Memoria QDR SRAM

Memoria DRAM

SPD de DRAM

Vínculos PCI Express conectados a FPGA

Datos Ethernet conectados a FPGA (interfaces QSFP)

E/S QSFP I2C

E/S PTP

Antes de poder ejecutar cualquier prueba o script, debe conectarse a la conexión de consola de la máquina virtual invitada. .

Están disponibles los siguientes conjuntos de pruebas:

prueba rápida: le permite realizar una prueba básica de todas las funciones asociadas a FPGA. Estas pruebas tardan uno o dos minutos en completarse.

burn-in: le permite ejercer toda la funcionalidad adjunta a FPGA. Estas pruebas tardan varias horas en completarse.

modo de prueba individual: permite probar un único subsistema con opciones de configuración adicionales.

Comando Ikondiag

Para ejecutar cualquiera de las pruebas, emita el ikondiag comando con los siguientes argumentos:

Antes de poder ejecutar las pruebas, debe conectarse a la conexión de consola de la máquina virtual invitada.

-t (prueba rápida | quemado | <nombre de la prueba>)

Este argumento identifica la prueba.

-h

Este argumento proporciona detalles de uso para la prueba.

-V

Este argumento proporciona resultados detallados para las pruebas.

Por ejemplo, para ejecutar la prueba PTP, ejecute el comando ikondiag -t PTP en el símbolo de la máquina virtual invitada:

ikondiag -t PTP

[2015-05-07 03:12:20][BEGIN TEST - PTP] ************************************************************************* PTP PHY interrupt: PASS 1G Ethernet PHY packet loopback test: PASS PTP clock generation/check: PASS UART (ToD) loopback: PASS ************************************************************************* [2015-05-07 03:13:30][END TEST PTP RESULT PASS]

Pruebas de funcionalidad básica

Puede probar la funcionalidad básica en la interfaz PCI Express y los componentes de memoria. Tabla 2 enumera los nombres de las pruebas y sus funciones.

Nombre de la prueba |

Description |

Detalles |

Argumentos opcionales |

Conjuntos de prueba |

Comportamiento de error |

|---|---|---|---|---|---|

FPGABasic |

Prueba el funcionamiento básico de FPGA. |

Configura la FPGA y lee algunos registros simples a través de PCI Express. |

Ninguno. |

Prueba rápida y quemado |

Cualquier error en esta prueba hace que el comando genere mensajes de ikondiag error y estado de prueba normales y, a continuación, finalice con otro mensaje de error. No puede continuar con las pruebas porque todas las pruebas dependen de la funcionalidad probada por esta. |

Pcie |

Verifica la funcionalidad y estabilidad de las transferencias masivas de datos PCIe. |

Devuelve repetidamente los datos pseudoaleatorios generados en la CPU a la FPGA y luego de vuelta a la CPU. Los datos devueltos se verifican en la CPU. |

-i <n> número de repeticiones (por defecto = 1 prueba rápida, 10.000 quemados) -j <n> tamaño de la transferencia individual en Mebibytes (valor predeterminado = 100 MiB). |

Prueba rápida y quemado |

Esta prueba notifica valores de datos erróneos y desplazamientos en la transferencia de datos. Cualquier error en esta prueba hará que el comando ikondiag genere mensajes de error y estado de prueba normales y luego terminará con un error adicional. No puede continuar con las pruebas adicionales porque todas las pruebas dependen de la funcionalidad probada por esta prueba. |

DIMM |

Comprueba la funcionalidad de consulta SPD y comprueba que están instalados los DIMM correctos. |

Lee datos del dispositivo SPD en módulos DIMM, informa del contenido y comprueba si hay valores erróneos y verifica:

|

Ninguno. |

Prueba rápida y quemado |

Si algún valor es inesperado, la prueba informa de valores erróneos y proporciona valores y rangos esperados. |

DRAMMemory |

Prueba la funcionalidad de transferencia de datos y la estabilidad de los dispositivos de memoria DRAM conectados a FPGA. |

|

-i <n> varía el número de iteraciones) predeterminado = 1 para prueba rápida, 500 para burn-in) |

Prueba rápida y quemado |

Esta prueba informa el número de errores durante la verificación. El número de errores se especifica como un número acumulado de errores por byte-lane y módulo DIMM. |

Pruebas y scripts de Ethernet

Las pruebas y scripts de Ethernet prueban los puertos C y el tráfico entre los puertos A y B. El tráfico entre los puertos A y B se prueba pasando los datos en los puertos F. Para los puertos C, debe retroceder el tráfico enviado en los puertos C. Puede utilizar cables de bucle invertido de cobre físicos para este propósito. Para los puertos F, , debe retroceder el tráfico enviado en los puertos F. Puede utilizar cables de bucle invertido de cobre para este propósito. Incluya los puertos F en una VLAN. Puede usar el script python PFAD_exec.py -t 1, así como las pruebas a continuación. El script python PFAD_exec.py -t 1 verifica el tráfico L2 de extremo a extremo en los puertos QSFP externos y comprueba las estadísticas de las interfaces de Junos OS y las estadísticas de las interfaces de la máquina virtual del software Packet Flow Diagnostics. Esta prueba fallará si se observa pérdida de tráfico en cualquiera de las interfaces. También hay una disposición para probar todas las combinaciones de puertos QSFP.

Tabla 3 enumera los nombres de las pruebas de Ethernet y sus funciones. Para obtener información acerca de cómo instalar la secuencia de comandos, consulte ../topic-map/packet-flow-accelerator-diagnostics-software.html#id-installing-packet-flow-accelerator-diagnostics-software.

Nombre de la prueba |

Description |

Detalles |

Argumentos opcionales |

Conjuntos de prueba |

Comportamiento de error |

|---|---|---|---|---|---|

QSFPEthernet |

Comprueba la funcionalidad de los vínculos Ethernet (QSFP). |

Genera, recibe y verifica que las tramas Ethernet tengan velocidad de línea a través del módulo FPGA. El contenido y la longitud de los paquetes consisten en datos pseudoaleatorios. Durante el funcionamiento, todas las conexiones QSFP se canalizan para utilizar 10 Gigabit Ethernet con los 32 canales Ethernet funcionando en paralelo en modo dúplex completo. |

-i <n> número variado de iteraciones (valor predeterminado = 1.000 para prueba rápida, 1e9 para burn-in) |

Prueba rápida y quemado |

Si se verifica que el número de paquetes enviados o recibidos correctamente no es igual, esta prueba se considera un fallo y se informan las discrepancias entre estas cantidades. Esta prueba falla si las conexiones Ethernet externas no están configuradas para circuito cerrado. |

QSFPI2C |

Comprueba si hay acceso a los cuatro módulos QSFP situados en la parte frontal del módulo QFX-PFA-4Q. |

Realiza lecturas de registros en los módulos I2C y verifica que los resultados sean los esperados. Para que esta prueba sea aprobada, los medios QSFP deben insertarse en los cuatro puertos del módulo QFX-PFA-4Q. Se puede utilizar cualquier tipo de medio externo (por ejemplo, cables DAC, bucle invertido de cobre, módulos y módulos ópticos). |

Ninguno. |

Prueba rápida y quemado |

Esta prueba falla si no puede detectar la presencia de un módulo QSFP o si los valores que lee son inesperados. |

Antes de poder ejecutar correctamente las pruebas y secuencias de comandos de Ethernet, debe realizar las siguientes tareas:

Realice un bucle externo de todas las conexiones Ethernet (QSFP) en el módulo QFX-PFA-4Q.

Para retroceder las interfaces QSFP en el módulo QFX-PFA-4Q, conecte módulos de bucle invertido de cobre en las cuatro interfaces QSFP+ instaladas en el módulo QFX-PFA-4Q.

Conecte módulos de bucle invertido de cobre en las interfaces QSFP+ (puertos 10 a 13) instaladas en el conmutador QFX5100-24Q-AA.

Canalizar los puertos 10 a 13 en el conmutador QFX5100-24Q-AA.

Empareje cada uno de los 16 carriles ikonDiag utilizando los nombres de interfaz Junos OS equivalentes con cada una de las interfaces Junos OS correspondientes que se canalizaron desde los puertos 10 a 13 del conmutador QFX5100-24Q-AA.

Nota:Cada VLAN debe ser independiente y contener exactamente dos puertos asociados: un puerto 10 Gigabit Ethernet que es un puerto F y un puerto 10 Gigabit Ethernet que es un puerto A.

Tabla 4 muestra las asignaciones para los canales de 10 Gigabit Ethernet en los puertos F del módulo QFX-PFA-4Q.

Tabla 4: Mapeos de canal Ethernet de 10 Gigabit en los puertos F del módulo QFX-PFA-4Q ikondiag Nombres

Description

JDFE_XE32_10G

xe-0/0/32

JDFE_XE33_10G

xe-0/0/33

JDFE_XE34_10G

xe-0/0/34

JDFE_XE35_10G

xe-0/0/35

JDFE_XE24_10G

xe-0/0/24

JDFE_XE25_10G

xe-0/0/25

JDFE_XE26_10G

xe-0/0/26

JDFE_XE27_10G

xe-0/0/27

JDFE_XE28_10G

xe-0/0/28

JDFE_XE29_10G

xe-0/0/29

JDFE_XE30_10G

xe-0/0/30

JDFE_XE31_10G

xe-0/0/31

JDFE_XE36_10G

xe-0/0/36

JDFE_XE37_10G

xe-0/0/37

JDFE_XE38_10G

xe-0/0/38

JDFE_XE39_10G

xe-0/0/39

Tabla 5 muestra las asignaciones para los canales de 10 Gigabit Ethernet en los puertos C del módulo QFX-PFA-4Q.

Tabla 5: Mapeos de canal Ethernet de 10 Gigabit en los puertos C del módulo QFX-PFA-4Q ikondiag Nombres

Description

JDFE_QSFP0_10G_PORT0

Puerto QSFP #0 Subcanal 0 de 10G

JDFE_QSFP0_10G_PORT1

Puerto QSFP #0 Subcanal 10G 1

JDFE_QSFP0_10G_PORT2

Puerto QSFP #0 10G subcanal 2

JDFE_QSFP0_10G_PORT3

Puerto QSFP #0 Subcanal 3 de 10G

JDFE_QSFP1_10G_PORT0

Puerto QSFP #1 10G subcanal 0

JDFE_QSFP1_10G_PORT1

Puerto QSFP #1 Subcanal 1 de 10G

JDFE_QSFP1_10G_PORT2

Puerto QSFP #1 Subcanal 2 de 10G

JDFE_QSFP1_10G_PORT3

Puerto QSFP #1 Subcanal 3 de 10G

JDFE_QSFP2_10G_PORT0

Puerto QSFP #2 Subcanal 0 de 10G

JDFE_QSFP2_10G_PORT1

Puerto QSFP #2 Subcanal 10G 1

JDFE_QSFP2_10G_PORT2

Puerto QSFP #2 Subcanal 2 de 10G

JDFE_QSFP2_10G_PORT3

Puerto QSFP #2 Subcanal 3 de 10G

JDFE_QSFP3_10G_PORT0

Puerto QSFP #3 Subcanal 0 de 10G

JDFE_QSFP3_10G_PORT1

Puerto QSFP #3 Subcanal 10G 1

JDFE_QSFP3_10G_PORT2

Puerto QSFP #3 Subcanal 2 de 10G

JDFE_QSFP3_10G_PORT3

Puerto QSFP #3 Subcanal 3 de 10G

Tabla 6 proporciona una conectividad exacta entre los puertos C y A.

Tabla 6: Conectividad exacta entre los puertos C y los puertos A Número de puerto QSFP

Número de canal

Interfaz de Junos OS

Puerto QSFP #0

Canal 0

xe-0/0/32

Puerto QSFP #0

Canal 1

xe-0/0/33

Puerto QSFP #0

Canal 2

xe-0/0/34

Puerto QSFP #0

Canal 3

xe-0/0/35

Puerto QSFP #1

Canal 0

xe-0/0/24

Puerto QSFP #1

Canal 1

xe-0/0/25

Puerto QSFP #1

Canal 2

xe-0/0/26

Puerto QSFP #1

Canal 3

xe-0/0/27

Puerto QSFP #2

Canal 0

xe-0/0/28

Puerto QSFP #2

Canal 1

xe-0/0/29

Puerto QSFP #2

Canal 2

xe-0/0/30

Puerto QSFP #2

Canal 3

xe-0/0/31

Puerto QSFP #3

Canal 0

xe-0/0/36

Puerto QSFP #3

Canal 1

xe-0/0/37

Puerto QSFP #3

Canal 2

xe-0/0/38

Puerto QSFP #3

Canal 3

xe-0/0/39

Agregue estas interfaces a una VLAN.

Canalizar los puertos 10 a 13 mediante la CLI de Junos.

Configure los puertos 10 a 13 en PIC 1 para que funcionen como puertos 10 Gigabit Ethernet.

[edit chassis fpc 0 pic 1] user@switch# set port-range 10 13 channel-speed 10g

Revise la configuración y ejecute el

commitcomando.[edit] user@switch# commit commit complete

Agregue las 16 interfaces canalizadas que acaba de configurar a 16 VLAN.

Para agregar las 16 interfaces canalizadas:

Cree 16 VLAN.

[edit vlans] user@switch# set v0_0 vlan-id 10 user@switch# set v0_1 vlan-id 11 user@switch# set v0_2 vlan-id 12 user@switch# set v0_3 vlan-id 13 user@switch# set v1_0 vlan-id 14 user@switch# set v1_1 vlan-id 15 user@switch# set v1_2 vlan-id 16 user@switch# set v1_3 vlan-id 17 user@switch# set v2_0 vlan-id 18 user@switch# set v2_1 vlan-id 19 user@switch# set v2_2 vlan-id 20 user@switch# set v2_3 vlan-id 21 user@switch# set v3_0 vlan-id 22 user@switch# set v3_1 vlan-id 23 user@switch# set v3_2 vlan-id 24 user@switch# set v3_3 vlan-id 25

Agregue las interfaces canalizadas a las VLAN.

[edit interfaces] user@switch# set xe-0/0/24 unit 0 family ethernet-switching vlan members v0_0 user@switch# set xe-0/0/25 unit 0 family ethernet-switching vlan members v0_1 user@switch# set xe-0/0/10:0 unit 0 family ethernet-switching vlan members v0_0 user@switch# set xe-0/0/10:1 unit 0 family ethernet-switching vlan members v0_1 user@switch# set xe-0/0/10:2 unit 0 family ethernet-switching vlan members v0_2 user@switch# set xe-0/0/10:3 unit 0 family ethernet-switching vlan members v0_3 user@switch# set xe-0/0/11:0 unit 0 family ethernet-switching vlan members v1_0 user@switch# set xe-0/0/11:1 unit 0 family ethernet-switching vlan members v1_1 user@switch# set xe-0/0/11:2 unit 0 family ethernet-switching vlan members v1_2 user@switch# set xe-0/0/11:3 unit 0 family ethernet-switching vlan members v1_3 user@switch# set xe-0/0/12:0 unit 0 family ethernet-switching vlan members v2_0 user@switch# set xe-0/0/12:1 unit 0 family ethernet-switching vlan members v2_1 user@switch# set xe-0/0/12:2 unit 0 family ethernet-switching vlan members v2_2 user@switch# set xe-0/0/12:3 unit 0 family ethernet-switching vlan members v2_3 user@switch# set xe-0/0/13:0 unit 0 family ethernet-switching vlan members v3_0 user@switch# set xe-0/0/13:1 unit 0 family ethernet-switching vlan members v3_1 user@switch# set xe-0/0/13:2 unit 0 family ethernet-switching vlan members v3_2 user@switch# set xe-0/0/13:3 unit 0 family ethernet-switching vlan members v3_3

Revise la configuración y ejecute el

commitcomando.[edit] user@switch# commit commit complete

Pruebas de esfuerzo

Las pruebas de esfuerzo ejercitan todas las E/S de alta velocidad en paralelo. Las pruebas de esfuerzo requieren el mismo medio externo que utilizó para las pruebas de Ethernet.Tabla 7 enumera el nombre de la prueba y sus funciones.

Nombre de la prueba |

Description |

Detalles |

Argumentos opcionales |

Conjuntos de prueba |

Comportamiento de error |

|---|---|---|---|---|---|

Estrés |

Ejercita todas las E/S de alta velocidad en paralelo. |

Ejerza todas las E/S de alta velocidad conectadas a la FPGA en paralelo, incluyendo:

Cada subsistema de prueba se ejerce de manera similar a las pruebas individuales descritas anteriormente. |

-i <n> número variado de iteraciones) predeterminado = 1 para prueba rápida, 1.000 para burn-in) |

Prueba rápida y quemado |

Si algún subsistema falla, la prueba se detiene. Se notifica el primer subsistema que se detectó que ha fallado. Nota:

Si se produce un error en varios subsistemas, solo se notificará el primer subsistema que haya fallado. |

Pruebas de PTP

Puede ejecutar PTP para hardware usado con PTP. Estas pruebas son útiles si está creando aplicaciones de temporización. Para ejecutar las pruebas, debe conectar cables Subminiatura versión B (SMB), cables de bucle invertido Ethernet y cables de bucle invertido ToD para la E/S de sincronización, el puerto serie ToD y los conectores 1 Gigabit Ethernet. Debe conectar los cables SMB, Ethernet y Bucle invertido ToD entre los conectores de salida y entrada 10M y PPS. El cable de circuito cerrado ToD es un cable RJ45 estándar con el Pin 3 (Tx Data) conectado al Pin 6 (Rx Data). Además de las pruebas de PTP, puede ejecutar scripts incluidos en el software Packet Flow Accelerator Diagnostics para probar PTP. Consulte Tabla 9 para obtener información sobre los scripts PTP. Los scripts PTP requieren que tenga instalada una imagen de Junos OS con automatización mejorada en el conmutador QFX5100-24Q-AA. Para obtener información acerca de cómo instalar las secuencias de comandos, consulte ../topic-map/packet-flow-accelerator-diagnostics-software.html#id-installing-packet-flow-accelerator-diagnostics-software.

Tabla 8 enumera los nombres de las pruebas PTP y sus funciones:

Nombre de la prueba |

Description |

Detalles |

Argumentos opcionales |

Conjuntos de prueba |

Comportamiento de error |

|---|---|---|---|---|---|

protocolo de tiempo de precisión (PTP) |

Comprueba la funcionalidad de varias funciones de sincronización de tiempo conectadas a FPGA del módulo QFX-PFA-4Q. |

Realiza varias pruebas sobre la funcionalidad de sincronización de tiempo del módulo QFX-PFA-4Q. Las subpruebas cubiertas por esta prueba incluyen:

|

Ninguno. |

Prueba rápida y quemado |

Un error en cualquiera de los subsistemas anteriores hace que se produzca un error en toda la prueba y genera un informe al final de la prueba que indica el estado de aprobación y reprobación de las subpruebas. |

Tabla 9 enumera el nombre de la secuencia de comandos y su función. Este script no forma parte del ikondiag comando. Puede ejecutar este comando Junos OS.

Nombre del script |

Description |

Detalles |

Argumentos opcionales |

Conjuntos de prueba |

Comportamiento de error |

|---|---|---|---|---|---|

./run_ptp_test |

Comprueba la funcionalidad de varias funciones de sincronización de tiempo conectadas a FPGA del módulo QFX-PFA-4Q. |

Realiza varias pruebas sobre la funcionalidad de sincronización de tiempo del módulo QFX-PFA-4Q. Las subpruebas cubiertas por esta prueba incluyen:

|

Ninguno. |

Ninguno. Esta prueba debe ejecutarse manualmente. |

Un error en cualquiera de los subsistemas anteriores hace que se produzca un error en toda la prueba y genera un informe al final de la prueba que indica el estado de aprobación y reprobación de las subpruebas. |

Pruebas LED del módulo QFX-PFA-4Q

Las pruebas de LED examinan los LED del módulo QFX-PFA-4Q.

Para ejecutar la prueba del LED, ejecute el ikon_led_toggle comando. La prueba puede tardar unos segundos en iniciarse porque se está configurando la FPGA. Cuando vea el mensaje Toggling LEDs. Send SIGINT (^C) to exit, comenzará la prueba. Para finalizar la prueba, escriba Ctrl-C. Tabla 10 enumera el nombre de la prueba y su función.

Nombre de la prueba |

Description |

Detalles |

Argumentos opcionales |

Conjuntos de prueba |

Comportamiento de error |

|---|---|---|---|---|---|

ikon_led_toggle |

Parpadea los LED del módulo QFX-PFA-4Q para una inspección visual. |

Los siguientes LED del módulo QFX-PFA-4Q pasarán repetidamente por los siguientes patrones: Nota:

Los LED AL y ST no se incluyen en esta prueba.

|

Ninguno. |

Ninguno. Esta prueba debe ejecutarse manualmente. |

Es posible que los LED no parpadeen. |

Utilidades de diagnóstico del acelerador de flujo de paquetes

Además de las pruebas del software de diagnóstico del acelerador de flujo de paquetes, hay utilidades incluidas en el software de diagnóstico del acelerador de flujo de paquetes que puede utilizar para diagnosticar problemas adicionales en el módulo QFX-PFA-4Q.

Antes de poder ejecutar las utilidades, debe conectarse a la consola de la máquina virtual invitada. Para obtener más información sobre cómo acceder a la máquina virtual invitada, consulte ../topic-map/packet-flow-accelerator-diagnostics-software.html#id-installing-packet-flow-accelerator-diagnostics-software.

Tabla 11 enumera el nombre de la utilidad y su función.

Nombre de la prueba |

Descripciones |

Detalles |

Resultado y comportamiento esperados |

|---|---|---|---|

maxtop |

Informa del estado de FPGA. |

Muestra información sobre el estado configurado actualmente del módulo FPGA y si el módulo está en funcionamiento. Comprueba que las operaciones básicas del controlador y del vínculo FPGA PCI Express funcionan correctamente. Si esta utilidad se cierra con un error o errores, es muy poco probable que otras operaciones de FPGA funcionen. |

La salida debe ser similar a la que se muestra a continuación. Si no se muestra este resultado, es posible que se produzca un error crítico en el entorno del software de diagnóstico o que el vínculo PCI Express a la FPGA no funcione.

|

ikon_snake |

Permite la conectividad snake entre todos los canales de 10 Gigabit Ethernet. |

Conecta el canal Rx de los 32 canales de 10 Gigabit Ethernet del módulo FPGA (interfaces QSFP) al canal Tx de la conexión vecina respectiva. Esto permite probar los 32 canales utilizando solo un generador de paquetes externo de interfaz 10 Gigabit Ethernet, módulos de bucle invertido de cobre y un cable de conexión QSFP <-> 4xSFP. |

Después de emitir esta prueba, todos los datos de Ethernet se reenviarán después de que se muestre el mensaje Nota:

Durante el tiempo antes de imprimir el mensaje de funcionamiento, es posible que el módulo FPGA esté en proceso de configuración, por lo que no se reenvían datos. Al presionar 'enter' saldrá de la utilidad. Una vez finalizada la prueba, los datos del paquete continúan reenviándose hasta que se ejecuta otra utilidad o prueba de Ethernet. |

ikon_eth_util todo --digitalloopback |

Permite el circuito cerrado digital en todas las interfaces de 10 Gigabit Ethernet en el Permite la conectividad "serpiente" entre todos los canales de 10 Gigabit Ethernet del módulo QFX-PFA-4Q. |

Conecta el lado Rx de todos los 32 canales de 10 Gigabit Ethernet del módulo FPGA (QSFP) al lado Tx del mismo canal. |

Después de realizar esta prueba, todos los datos de Ethernet se reenviarán como se describe después de que se muestre el mensaje Nota:

Antes de que se muestre el mensaje de funcionamiento, es posible que el módulo FPGA esté en proceso de configuración y no se reenvíen datos. Al presionar Intro, se cierra la utilidad. Una vez finalizada la prueba, los datos del paquete continúan reenviándose hasta que se ejecuta otra utilidad o prueba de Ethernet. |

ikon_eth_util |

Permite que los datos pasen a través de los puertos QSFP del módulo QFX-PFA-4Q. |

Permite que los datos pasen a través de los puertos QSFP del módulo QFX-PFA-4Q en el módulo QFX-PFA-4Q. Nota:

Dado que todos los puertos QSFP se canalizan a 10 Gigabit Ethernet, debe utilizar cables de conexión SFP al conectar medios externos. |

Después de realizar esta prueba, todos los datos de Ethernet se reenvían como se describe después de que aparezca el mensaje ' en ejecución, presione la tecla Retorno para salir '. Nota:

Antes de que aparezca el mensaje de funcionamiento, es posible que el módulo FPGA esté en proceso de configuración y no se reenvíen datos. Al presionar 'enter' saldrá de la utilidad. Una vez finalizada la prueba, los datos del paquete seguirán reenviándose hasta que se ejecute otra utilidad o prueba de Ethernet. |

maxnet -v enlace mostrar |

Volca las estadísticas de paquetes FPGA. |

Muestra estadísticas sobre los paquetes enviados y recibidos en todos los vínculos (QSFP) desde los núcleos IP MAC y PHY de la FPGA. El uso de la opción 'v' proporciona una salida detallada. Aquí hay algunos elementos importantes a tener en cuenta:

|

El resultado de ejemplo para un único vínculo de 10 Gigabit Ethernet es el siguiente: MaxTop Tool 2015.1

Found 1 card(s) running MaxelerOS 2015.1

Card 0: QFX-PFA-4Q (P/N: 241124) S/N: 96362301684266423 Mem: 24GB

Load average: 0.00, 0.00, 0.00

DFE %BUSY TEMP MAXFILE PID USER TIME COMMAND

0 0.0% - 2fcf249cc7... - - - -

|

host2mem I <filename> -o <filename> -t <DDR | QDR0 | QDRPARITY0 | QDR1 | QDRPARITY1> |

Escribe y, a continuación, lee datos arbitrarios de QDR SRAM o DRAM. |

Funciona transmitiendo el contenido de un archivo binario a uno de los recursos de memoria del módulo QFX-PFA-4Q a través de la FPGA y, a continuación, transmite los mismos datos desde la memoria a otro archivo. Nota:

No puede leer solo datos de RAM porque el contenido no se conserva entre la ejecución de varias pruebas. |

Informa APROBADO o FALLIDO dependiendo de si los datos devueltos coinciden con los datos de entrada. |

Tabla 12 enumera los argumentos de la línea de comandos para la utilidad host2mem.

Argumento |

Description |

|---|---|

-- ayuda | -h |

Imprima el uso y salga. |

-i <archivo de entrada> |

Archivo de datos de entrada. |

-o <archivo de salida> |

Archivo de datos de salida. |

-- prueba | -t <nombre de prueba> |

Recurso de prueba. Consulte Tabla 13 para obtener información sobre los recursos. |

-- detallado | -v |

Habilite el modo detallado. |

El formato de archivo para los archivos de entrada y salida es idéntico. Los datos se empaquetan consecutivamente como palabras según el ancho especificado en la tabla de modo de prueba a continuación. El tamaño de un archivo de entrada puede ser menor, pero no debe superar el tamaño total del recurso que se está probando. El tamaño del archivo de salida es el mismo que el del archivo de entrada y, siempre que no haya errores, tiene el mismo contenido.

Modo de prueba |

Recurso |

Ancho de palabra |

Tamaño de los datos de prueba |

|---|---|---|---|

DDR |

DDR SDRAM |

192 B |

24 GB |

QDR0 |

Datos QDR0 |

16 B |

32 MB |

QDRPARITY0 |

Bits de paridad QDR0 |

2 B |

4 MB |

QDR1 |

Datos QDR1 |

16 B |

32 MB |

QDRPARITY1 |

Bits de paridad QDR1 |

2 B |

4 MB |

La memoria dinámica de acceso aleatorio (DRAM) del módulo QFX-PFA-4Q contiene tres módulos de memoria en línea duales (DIMM3, DIMM4, DIMM6), y cada palabra de datos se divide en los tres DIMM.Tabla 14 enumera la asignación de bytes a DIMM.

0 |

DIMM3 |

63 |

64 |

DIMM4 |

127 |

128 |

DIMM6 |

191 |

Resultado de ejemplo para el software de diagnóstico del acelerador de paquetes

En esta sección se proporcionan algunos resultados de ejemplo para pruebas básicas, pruebas de Ethernet, pruebas de PTP y utilidades.

ikondiag -t FPGABasic

[2015-05-07 03:00:17][BEGIN TEST - FPGABasic] [2015-05-07 03:00:17][END TEST FPGABasic RESULT PASSED]

ikondiag -t DIMM

[2015-05-07 03:01:09][BEGIN TEST - DIMM] [2015-05-07 03:01:09][END TEST DIMM RESULT PASSED]

ikondiag -t QSFPEthernet

[2015-05-07 03:02:33][BEGIN TEST - QSFPEthernet] *********************************************** Test Failed: QSFP0_10G_PORT0: FAIL - packets received = 0/1000 QSFP0_10G_PORT1: FAIL - packets received = 0/1000 QSFP0_10G_PORT2: FAIL - packets received = 0/1000 QSFP0_10G_PORT3: FAIL - packets received = 0/1000 QSFP1_10G_PORT0: FAIL - packets received = 0/1000 QSFP1_10G_PORT1: FAIL - packets received = 0/1000 QSFP1_10G_PORT2: FAIL - packets received = 0/1000 QSFP1_10G_PORT3: FAIL - packets received = 0/1000 QSFP2_10G_PORT0: FAIL - packets received = 0/1000 QSFP2_10G_PORT1: FAIL - packets received = 0/1000 QSFP2_10G_PORT2: FAIL - packets received = 0/1000 QSFP2_10G_PORT3: FAIL - packets received = 0/1000 QSFP3_10G_PORT0: FAIL - packets received = 0/1000 QSFP3_10G_PORT1: FAIL - packets received = 0/1000 QSFP3_10G_PORT2: FAIL - packets received = 0/1000 QSFP3_10G_PORT3: FAIL - packets received = 0/1000 QSFP4_10G_PORT0: PASS - packets received = 1000/1000 QSFP4_10G_PORT1: PASS - packets received = 1000/1000 QSFP4_10G_PORT2: PASS - packets received = 1000/1000 QSFP4_10G_PORT3: PASS - packets received = 1000/1000 QSFP5_10G_PORT0: PASS - packets received = 1000/1000 QSFP5_10G_PORT1: PASS - packets received = 1000/1000 QSFP5_10G_PORT2: PASS - packets received = 1000/1000 QSFP5_10G_PORT3: PASS - packets received = 1000/1000 QSFP6_10G_PORT0: PASS - packets received = 1000/1000 QSFP6_10G_PORT1: PASS - packets received = 1000/1000 QSFP6_10G_PORT2: PASS - packets received = 1000/1000 QSFP6_10G_PORT3: PASS - packets received = 1000/1000 QSFP7_10G_PORT0: PASS - packets received = 1000/1000 QSFP7_10G_PORT1: PASS - packets received = 1000/1000 QSFP7_10G_PORT2: PASS - packets received = 1000/1000 QSFP7_10G_PORT3: PASS - packets received = 1000/1000 *********************************************** [2015-05-07 03:02:41][END TEST QSFPEthernet RESULT PASSED]

ikondiag -t DRAMMemory -i 3

[2015-05-07 03:03:37][BEGIN TEST - DRAMMemory] [2015-05-07 03:04:21][END TEST DRAMMemory RESULT PASSED]

ikondiag -t QDRMemory -p -i 3

[2015-05-07 03:10:38][BEGIN TEST - QDRMemory] [2015-05-07 03:10:45][END TEST QDRMemory RESULT PASSED]

ikondiag -t Estrés -p -i 10

[2015-05-07 03:11:24][BEGIN TEST - Stress] *********************************************** Test Failed: QSFP0_10G_PORT0: PASS - packets received = 650000/650000 QSFP0_10G_PORT1: PASS - packets received = 650000/650000 QSFP0_10G_PORT2: PASS - packets received = 650000/650000 QSFP0_10G_PORT3: PASS - packets received = 650000/650000 QSFP1_10G_PORT0: PASS - packets received = 650000/650000 QSFP1_10G_PORT1: PASS - packets received = 650000/650000 QSFP1_10G_PORT2: PASS - packets received = 650000/650000 QSFP1_10G_PORT3: PASS - packets received = 650000/650000 QSFP2_10G_PORT0: PASS - packets received = 650000/650000 QSFP2_10G_PORT1: PASS - packets received = 650000/650000 QSFP2_10G_PORT2: PASS - packets received = 650000/650000 QSFP2_10G_PORT3: PASS - packets received = 650000/650000 QSFP3_10G_PORT0: PASS - packets received = 650000/650000 QSFP3_10G_PORT1: PASS - packets received = 650000/650000 QSFP3_10G_PORT2: PASS - packets received = 650000/650000 QSFP3_10G_PORT3: PASS - packets received = 650000/650000 QSFP4_10G_PORT0: PASS - packets received = 650000/650000 QSFP4_10G_PORT1: PASS - packets received = 650000/650000 QSFP4_10G_PORT2: PASS - packets received = 650000/650000 QSFP4_10G_PORT3: PASS - packets received = 650000/650000 QSFP5_10G_PORT0: PASS - packets received = 650000/650000 QSFP5_10G_PORT1: PASS - packets received = 650000/650000 QSFP5_10G_PORT2: PASS - packets received = 650000/650000 QSFP5_10G_PORT3: PASS - packets received = 650000/650000 QSFP6_10G_PORT0: PASS - packets received = 650000/650000 QSFP6_10G_PORT1: PASS - packets received = 650000/650000 QSFP6_10G_PORT2: PASS - packets received = 650000/650000 QSFP6_10G_PORT3: PASS - packets received = 650000/650000 QSFP7_10G_PORT0: PASS - packets received = 650000/650000 QSFP7_10G_PORT1: PASS - packets received = 650000/650000 QSFP7_10G_PORT2: PASS - packets received = 650000/650000 QSFP7_10G_PORT3: PASS - packets received = 650000/650000 ***********************************************

ikondiag -t PTP

[2015-05-07 03:12:20][BEGIN TEST - PTP] ************************************************************************* PTP PHY interrupt: PASS 1G Ethernet PHY packet loopback test: PASS PTP clock generation/check: PASS UART (ToD) loopback: PASS ************************************************************************* [2015-05-07 03:13:30][END TEST PTP RESULT PASS]

ikondiag -t Application -i 2

iterations = 2 [2015-05-07 03:14:11][BEGIN TEST - Application Test] [2015-05-07 03:17:33][END TEST Application Test RESULT PASSED]

maxtop

MaxTop Tool 2015.1 Found 1 card(s) running MaxelerOS 2015.1 Card 0: (P/N: 241124) S/N: 96362301684266423 Mem: 24GB Load average: 0.00, 0.00, 0.00 DFE %BUSY TEMP MAXFILE PID USER TIME COMMAND 0 0.0% - 7e2198e5c0... - - - -

ikon_eth_util --all-pass-through

Ikon Ethernet Pass Through Utility setting portConnect_QSFP4_10G_PORT0_QSFP0_10G_PORT0 to 1 setting portConnect_QSFP4_10G_PORT1_QSFP0_10G_PORT1 to 1 setting portConnect_QSFP4_10G_PORT2_QSFP0_10G_PORT2 to 1 setting portConnect_QSFP4_10G_PORT3_QSFP0_10G_PORT3 to 1 setting portConnect_QSFP1_10G_PORT0_QSFP5_10G_PORT0 to 1 setting portConnect_QSFP1_10G_PORT1_QSFP5_10G_PORT1 to 1 setting portConnect_QSFP1_10G_PORT2_QSFP5_10G_PORT2 to 1 setting portConnect_QSFP1_10G_PORT3_QSFP5_10G_PORT3 to 1 setting portConnect_QSFP2_10G_PORT0_QSFP6_10G_PORT0 to 1 setting portConnect_QSFP2_10G_PORT1_QSFP6_10G_PORT1 to 1 setting portConnect_QSFP2_10G_PORT2_QSFP6_10G_PORT2 to 1 setting portConnect_QSFP2_10G_PORT3_QSFP6_10G_PORT3 to 1 setting portConnect_QSFP3_10G_PORT0_QSFP7_10G_PORT0 to 1 setting portConnect_QSFP3_10G_PORT1_QSFP7_10G_PORT1 to 1 setting portConnect_QSFP3_10G_PORT2_QSFP7_10G_PORT2 to 1 setting portConnect_QSFP3_10G_PORT3_QSFP7_10G_PORT3 to 1 running press return key to exit