Correction d’erreur directe (FEC) et taux d’erreur binaire (BER)

Les interfaces de réseau de transport optique (OTN) utilisent le taux d’erreur binaire (BER) de la correction d’erreur avant transfert (pré-FEC) pour surveiller l’état d’une liaison OTN. Utilisez cette rubrique pour en savoir plus sur la façon dont les liaisons OTN sont surveillées et sur les modes FEC pris en charge sur les périphériques.

Présentation

Les interfaces optiques sur PTX Series Routeurs de transport de paquets permettent de surveiller l’état d’une liaison optique à l’aide du taux d’erreur binaire (BER) de la correction d’erreur avant transfert (pré-FEC). Les PICs suivants prennent en charge la surveillance du TEB avant la FEC :

P1-PTX-2-100G-WDM

P2-100GE-OTN

P1-PTX-24-10G-W-SFPP

Les PICs utilisent la correction d’erreur directe (FEC) pour corriger les erreurs binaires dans les données reçues. Tant que le TEB pré-FEC est inférieur à la limite FEC, toutes les erreurs binaires sont identifiées et corrigées avec succès et, par conséquent, aucune perte de paquet ne se produit. Le système surveille le TEB pré-FEC sur chaque port. Cela donne un avertissement précoce de la dégradation de la liaison. En configurant un seuil et un intervalle de TEB pré-FEC appropriés, vous permettez au PIC de prendre des mesures préventives avant que la limite FEC ne soit atteinte. Si cette logique de seuil BER pré-FEC est associée à un reroutage rapide MPLS, la perte de paquets peut être minimisée ou empêchée.

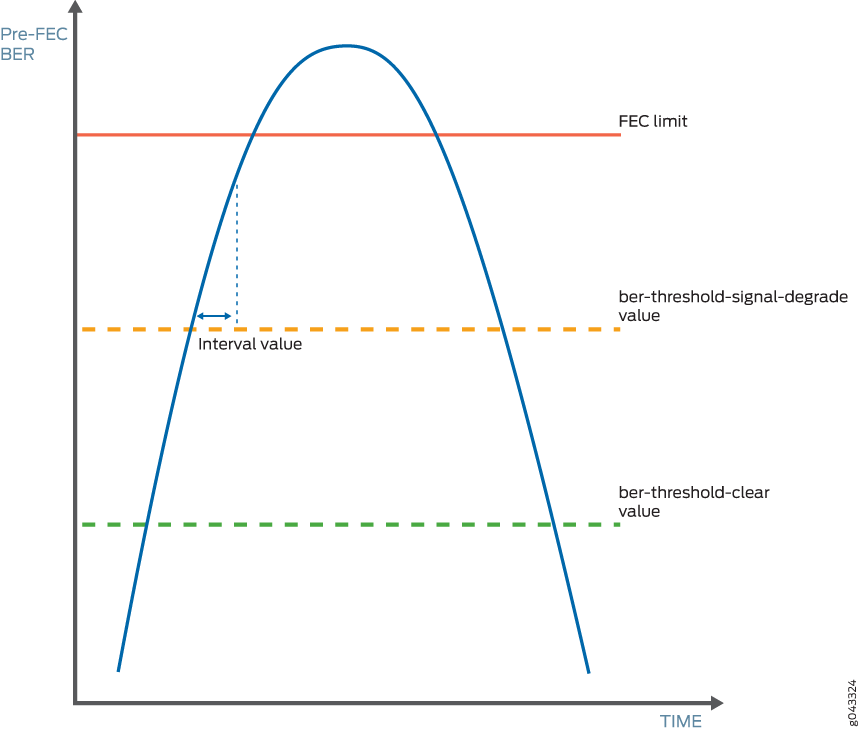

Vous devez spécifier à la fois le seuil de dégradation du signal (ber-threshold-signal-degrade) et l’intervalle (interval) de l’interface. Le seuil définit les critères du TEB pour une condition de dégradation du signal et l’intervalle définit la durée minimale pendant laquelle le TEB doit dépasser le seuil avant qu’une alarme ne soit déclenchée. La relation entre le seuil et l’intervalle est illustrée par Figure 1. Après le déclenchement d’une alarme, si le TEB revient à un niveau inférieur à la valeur seuil d’effacement (ber-threshold-clear), l’alarme est effacée.

Lorsque la surveillance du TEB pré-FEC est activée, lorsque le seuil de dégradation du signal pré-FEC configuré est atteint, le PIC arrête de transférer les paquets vers l’interface distante et déclenche une alarme d’interface. Les paquets entrants continuent d’être traités. Si la surveillance du TEB antérieur à la FEC est utilisée avec le reroutage rapide MPLS ou une autre méthode de protection de liaison, le trafic est redirigé vers une autre interface.

Vous pouvez également configurer le reroutage rapide vers l’arrière pour insérer l’état pré-FEC local dans les trames optiques transmises, informant ainsi l’interface distante de la dégradation du signal. L’interface distante peut utiliser ces informations pour réacheminer le trafic vers une autre interface. Si vous utilisez la surveillance du TEB pré-FEC avec le reroutage rapide vers l’arrière, la notification de la dégradation du signal et du réacheminement du trafic se produit en moins de temps que ce qui est requis par un protocole de couche 3.

Incluez les signal-degrade-monitor-enable instructions et au niveau de la hiérarchie pour permettre la [edit interfaces interface-name otn-options preemptive-fast-reroute] surveillance du TEB pré-FEC et backward-frr-enable le reroutage rapide vers l’arrière.

Lorsque vous configurez la surveillance de la dégradation du signal avant la FEC TEB, nous vous recommandons de configurer à la fois les instructions et signal-degrade-monitor-enable .backward-frr-enable

Vous pouvez également configurer les seuils BER pré-FEC qui déclenchent ou effacent une alarme de dégradation du signal et l’intervalle de temps pour les seuils. Si les seuils et l’intervalle du TEB ne sont pas configurés, les valeurs par défaut sont utilisées.

Lorsqu’une alarme de dégradation du signal reçu est active et que le reroutage rapide vers l’arrière est activé, un indicateur spécifique est inséré dans la surcharge optique transmise. Le PIC distant situé à l’extrémité opposée de la liaison surveille le module optique au-dessus de la tête, permettant ainsi aux deux extrémités d’initier un réacheminement du trafic en cas de dégradation du signal. Lorsque la condition de dégradation du signal est effacée, l’indicateur de surcharge revient à un état normal.

La valeur du seuil de dégradation du signal avant la FEC définit une quantité spécifique de marge du système par rapport à la limite de correction du TEB (ou limite FEC) du décodeur FEC de réception du PIC. Chaque PIC a une limite FEC définie : elle est intrinsèque à l’implémentation du décodeur FEC.

Les exemples ci-dessous utilisent des mesures à2 facteurs Q (également connus sous le nom de facteur Q). Le facteur Q 2 est exprimé en décibels par rapport à un facteur Q2 de zéro (dBQ). Le facteur Q2 vous permet de décrire la marge du système en termes linéaires, contrairement aux valeurs du TEB, qui sont de nature non linéaire. Une fois que vous avez déterminé les seuils, vous devez convertir les valeurs de seuil du facteur Q2 en BER pour les entrer dans la CLI à l’aide de la notation scientifique. Le TEB peut être converti en facteur Q2 à l’aide de l’équation suivante :

Q2-factor = 20 * log10 (sqrt(2) * erfcinv(2 * BER))

Pour effectuer une conversion entre le facteur Q2 et le TEB dans un tableur, vous pouvez approximer les valeurs à l’aide des formules suivantes :

Pour calculer le facteurQ 2 :

= 20 * LOG10(–NORMSINV(BER))

Pour calculer le TEB :

= 1 – NORMSDIST(10^(0.05 * Q2-factor))

Incluez les instructions , ber-threshold-clear, et au niveau de la hiérarchie pour configurer les ber-threshold-signal-degradeseuils et interval l’intervalle de [edit interfaces interface-name otn-options signal-degrade] temps du TEB.

La configuration d’un seuil de TEB élevé pour la dégradation du signal et d’un intervalle long peut entraîner une saturation du registre interne du compteur. Une telle configuration est ignorée par le routeur et les valeurs par défaut sont utilisées à la place. Un message de journal système est enregistré pour cette erreur.

Dégrader et effacer les valeurs seuils du signal pour les PIC

Tableau 1 montre la relation entre la limite FEC fixe, le seuil configurable de dégradation du signal et le seuil de dégagement configurable pour différents PICs. Dans cet exemple, environ 1 dBQ de marge système a été définie entre la limite FEC, le seuil de dégradation du signal et le seuil de dégagement.

|

PIC |

FEC Type |

Limite FEC |

Seuil de dégradation du signal |

Effacer le seuil |

|||

|---|---|---|---|---|---|---|---|

| Q2-Facteur | BER | Q2-Facteur | BER | Q2-Facteur | BER | ||

|

P1-PTX-2-100G-WDM |

Le SD-FEC |

6,7 dBQ |

1.5E–2 |

7,7 dBQ |

7.5E–3 |

8,7 dBQ |

3.0E–3 |

|

P2-100GE-OTN |

G.709 GFEC |

11,5 dBQ |

8.0E–5 |

12,5 dBQ |

1.1E–5 |

13,5 dBQ |

1.0E–6 |

|

P1-PTX-24-10G-W-SFPP |

G.975.1 I.4 (UFEC) |

9,1 dBQ |

2.2E–3 |

10,1 dBQ |

6.9E–4 |

11,1 dBQ |

1.6E–4 |

|

G.975.1 I.7 (EFEC) |

9,6 dBQ |

1.3E–3 |

10,6 dBQ |

3.6E–4 |

11,6 dBQ |

7.5E–5 |

|

|

G.709 GFEC |

11,5 dBQ |

8.0E-5 |

12,5 dBQ |

1.1E-5 |

13,5 dBQ |

1,0E à 6 |

|

Pour ajuster le seuil de dégradation du signal, vous devez d’abord décider d’une nouvelle cible de marge du système, puis calculer la valeur du TEB correspondante (à l’aide de l’équation permettant de convertir le facteur Q2 en TEB). Tableau 2 affiche les valeurs si une marge système de 3 dBQ par rapport à la limite FEC est requise pour le seuil de dégradation du signal (tout en maintenant le seuil de dégagement à 1 dBQ par rapport au seuil de dégradation du signal).

Le choix de la marge système est subjectif, car vous souhaiterez peut-être optimiser vos seuils en fonction de différentes caractéristiques de liaison et d’objectifs de tolérance de panne et de stabilité. Pour plus d’informations sur la configuration de la surveillance du TEB pré-FEC et des seuils du TEB, contactez votre représentant Juniper Networks.

|

PIC |

FEC Type |

Limite FEC |

Seuil de dégradation du signal |

Effacer le seuil |

|||

|---|---|---|---|---|---|---|---|

| Q2-Facteur | BER | Q2-Facteur | BER | Q2-Facteur | BER | ||

|

P1-PTX-2-100G-WDM |

Le SD-FEC |

6,7 dBQ |

1.5E–2 |

9,7 dBQ |

1.1E–3 |

10,7 dBQ |

2.9E–4 |

|

P2-100GE-OTN |

G.709 GFEC |

11,5 dBQ |

8.0E-5 |

14,5 dBQ |

4.9E–8 |

15,5 dBQ |

1.1E–9 |

|

P1-PTX-24-10G-W-SFPP |

G.975.1 I.4 (UFEC) |

9,1 dBQ |

2.2E–3 |

12,1 dBQ |

2.8E–5 |

13,1 dBQ |

3.1E–6 |

|

G.975.1 I.7 (EFEC) |

9,6 dBQ |

1.3E-3 |

12,6 dBQ |

1.1E-5 |

13,6 dBQ |

9.1E–7 |

|

|

G.709 GFEC |

11,5 dBQ |

8.0E-5 |

14,5 dBQ |

4.8E–8 |

15,5 dBQ |

1.1E-9 |

|

Modes de correction d’erreur directe pris en charge

Cette section décrit les modes FEC pris en charge sur les [edit interfaces interface-name otn-options] différents routeurs au niveau.

Routeurs MX Series

|

Carte de ligne |

FEC Mode |

Vitesse du port |

|---|---|---|

|

|

10G |

|

|

|

10G et 100G (GFEC uniquement) |

|

|

|

Le 10G |

|

|

|

100G (GFEC uniquement) |

|

|

|

100G |

Routeurs PTX Series

|

Carte de ligne |

FEC Mode | Vitesse du port |

|---|---|---|

| P1-PTX-24-10G-W-SFPP |

(GFEC | EFEC | Aucun | UFEC) |

Le 10G |

| P2-10G-40G-QSFPP |

(GFEC | EFEC | Aucun | UFEC) |

Le 10G |

| P2-100GE-OTN |

(GFEC | Aucune) |

100G (GFEC uniquement) |

| P1-PTX-2-100G-WDM |

(gfec-sdfec) |

100G |

| PTX-5-100G-WDM |

(GFEC | SDFEC) |

100G |

Voir également

Modes de correction d’erreur directe pris en charge sur les routeurs PTX Series

Tableau 6 répertorie les modes FEC pris en charge sur les routeurs PTX Series au niveau de la [edit interfaces interface-name otn-options] hiérarchie.

Carte de ligne |

FEC Mode |

Vitesse du port |

Junos Version |

|---|---|---|---|

|

10G |

12.1X48, 12.3, 13.2 (PTX5000)13.2R2 (PTX3000) |

|

|

Le 10G |

14.1R2 (PTX5000)15.1F6 (PTX3000) |

|

|

100G (GFEC uniquement) |

14.1 |

|

|

100G |

13.2 (PTX5000)13.3 (PTX3000) |

|

|

100G |

15.1F6 |

Voir également

Modes de correction d’erreur directe pris en charge sur ACX6360 routeur

Tableau 7 répertorie les modes FEC pris en charge sur ACX6360 routeurs au niveau de la [edit interfaces interface-name optics-options] hiérarchie.

FEC Mode |

Modulation Format |

Vitesse du port |

Junos Version |

|---|---|---|---|

|

QPSK |

100G |

18.3R1 |

|

QPSK |

100G |

18.3R1 |

|

8-MAQ |

200G |

18.3R1 |

|

16-QAM |

200G |

18.3R1 |

Voir également

Modes FEC pris en charge sur les routeurs ACX5448-D

Tableau 8 répertorie les modes de correction d’erreur directe (FEC) pris en charge sur les routeurs ACX5448-D. Vous pouvez configurer les modes FEC au niveau de la [edit interfaces interface-name optics-options] hiérarchie.

FEC Mode |

Modulation Format |

Vitesse du port |

Junos OS |

|---|---|---|---|

|

QPSK |

100 Gbit/s |

19.2R1-S1 |

|

QPSK |

100 Gbit/s |

19.2R1-S1 |

|

QPSK |

100 Gbit/s |

19.2R1-S1 |

|

8-MAQ |

200 Gbit/s |

19.2R1-S1 |

|

16-QAM |

200 Gbit/s |

19.2R1-S1 |

Voir également

Tableau de l'historique des modifications

La prise en charge des fonctionnalités est déterminée par la plateforme et la version que vous utilisez. Utilisez l' Feature Explorer pour déterminer si une fonctionnalité est prise en charge sur votre plateforme.