Software de diagnóstico do Packet Flow Accelerator e outras concessionárias

Você pode usar o software Packet Flow Accelerator Diagnostics para validar a integridade do módulo QFX-PFA-4Q e do switch QFX5100-24Q-AA. O software Packet Flow Accelerator Diagnostics contém diagnósticos padrão, diagnósticos de orquestração, protocolo de tempo de precisão (PTP) e diagnósticos de sincronização, e outros serviços de utilidade. O software Packet Flow Accelerator Diagnostics é executado em uma máquina virtual convidada (VM) no switch QFX5100-24Q-AA e exige que você configure opções de VM convidados no Junos OS CLI.

O módulo QFX-PFA-4Q contém quatro interfaces QSFP+ Ethernet QSFP+ de 40 Gigabits, um módulo FPGA e interfaces de temporizações de entrada e saída para oferecer suporte a aplicativos de protocolo de tempo de precisão. O módulo FPGA contém uma lógica que você pode personalizar para processar transações de alto volume, sensíveis à latência e intensivas em computação.

Antes de poder executar o software e os serviços de diagnóstico do Packet Flow Accelerator, certifique-se de ter realizado as seguintes tarefas:

Verifique se você instalou o módulo QFX-PFA-4Q instalado no switch QFX5100-24Q-AA. Para obter mais informações, veja Instalação de um módulo de expansão em um dispositivo de QFX5100

Certifique-se de ter o Junos OS Release 14.1X53-D27 com automação aprimorada instalada no switch QFX5100-24Q-AA. Para obter mais informações, veja Instalação de pacotes de software em dispositivos da Série QFX.

Instale o software Packet Flow Accelerator Diagnostics. Para obter mais informações, veja ../topic-map/packet-flow-accelerator-diagnostics-software.html#id-installing-packet-flow-accelerator-diagnostics-software.

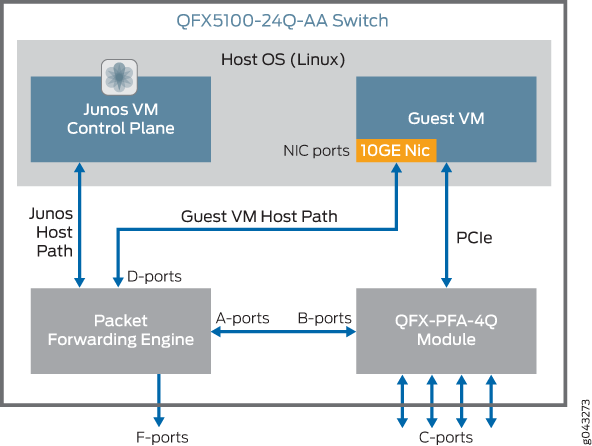

Portas externas e internas e portas de placa de interface de rede

O software e as concessionárias Packet Flow Accelerator Diagnostics validam os caminhos de dados entre as portas externas e internas no switch QFX5100-24Q-AA e no módulo QFX-PFA-4Q. Figura 1 ilustra os nomes das portas no switch QFX5100-24Q-AA e no módulo QFX-PFA-4Q e como elas se conectam.

Tabela 1 fornece informações sobre as portas externas e internas e portas NIC no switch QFX5100-24Q-AA e no módulo QFX-PFA-4Q.

Portas A |

Interfaces xe-0/0/24 a xe-0/0/39 no mecanismo de encaminhamento de pacotes (PFE) do switch QFX5100-24Q-AA conectam-se às portas B no módulo FPGA no módulo de expansão QFX-PFA-4Q. As portas A exigem portas B correspondentes no módulo FPGA. Você pode gerenciar essas interfaces através do Junos OS. |

Portas B |

As portas Ethernet internas de 10 Gigabit se conectam ao módulo FPGA no módulo QFX-PFA-4Q, que depois se conectam às portas A no PFE do switch QFX5100-24Q-AA. A convenção de nomeação para essas portas é determinada pelo VM convidado. O VM convidado controla o módulo FPGA. |

Portas C |

Quatro portas Ethernet de 40 Gigabit voltadas para a frente no módulo QFX-PFA-4Q conectam-se ao módulo FPGA em execução no switch QFX5100-24Q-AA e nas portas F no switch QFX5100-24Q-AA. O VM convidado controla o módulo FPGA. |

Portas D |

Duas portas internas Ethernet de 10 Gigabit no mecanismo de encaminhamento de pacotes do switch QFX5100-24Q-AA conectam-se à NIC Ethernet no switch QFX5100-24Q-AA. A convenção de nomeação para essas portas é a mesma usada para as portas F. Você pode gerenciar essas portas através do Junos OS. |

Portas F |

Vinte e quatro portas Ethernet de 40 Gigabit voltadas para a frente no switch QFX5100-24Q-AA. Essas portas contêm um prefixo "et" quando estão no modo Ethernet de 40 Gigabits. Se você canalizar essas interfaces, o prefixo é "xe". Você pode gerenciar essas portas através do Junos OS. |

Portas NIC |

Interfaces internas xe-0/0/40 e xe-0/0/41 no switch QFX5100-24Q-AA conectam-se ao PFE para uso no VM convidado. As portas NIC executam as mesmas funções que qualquer outra porta NIC do Linux OS. As portas NIC não funcionam a menos que o módulo QFX-OS-4Q seja instalado. |

Testes e scripts de software do Packet Flow Accelerator Diagnostics

Você pode executar o software Packet Flow Accelerator Diagnostics para testar os seguintes subsistemas no módulo QFX-PFA-4Q:

FPGA

Memória QDR SRAM

Memória DRAM

DRAM SPDs

Links PCI Express conectados por FPGA

Dados Ethernet conectados por FPGA (interfaces QSFP)

E/S QSFP I2C

E/S de PTP

Antes de realizar qualquer teste ou script, você precisa se conectar à conexão de console do VM convidado. .

Os seguintes conjuntos de testes estão disponíveis:

teste rápido — permite que você realize um teste básico de todas as funcionalidades anexadas ao FPGA. Esses testes levam um ou dois minutos para serem concluídos.

burn-in — permite que você exerça todas as funcionalidades anexadas ao FPGA. Esses testes levam várias horas para serem concluídos.

modo de teste individual — permite testar um único subsistema com opções de configuração extras.

Comando Ikondiag

Para executar qualquer um dos testes, emita o ikondiag comando com os seguintes argumentos:

Antes de realizar os testes, você precisa se conectar à conexão de console do VM convidado.

t (teste rápido | burn-in | <est name>)

Esse argumento identifica o teste.

-h

Esse argumento fornece detalhes de uso para o teste.

-V

Esse argumento fornece saída verbosa para os testes.

Por exemplo, para realizar o teste de PTP, emita o comando ikondiag-t PTP no prompt de VM convidado:

ikondiag -t PTP

[2015-05-07 03:12:20][BEGIN TEST - PTP] ************************************************************************* PTP PHY interrupt: PASS 1G Ethernet PHY packet loopback test: PASS PTP clock generation/check: PASS UART (ToD) loopback: PASS ************************************************************************* [2015-05-07 03:13:30][END TEST PTP RESULT PASS]

Testes básicos de funcionalidade

Você pode testar a funcionalidade básica na interface PCI Express e componentes de memória. Tabela 2 lista os nomes dos testes e suas funções.

Nome do teste |

Descrição |

Detalhes |

Argumentos opcionais |

Conjuntos de testes |

Comportamento de falha |

|---|---|---|---|---|---|

FPGABasic |

Testa a operação básica de FPGA. |

Configura o FPGA e lê alguns registros simples no PCI Express. |

Nenhum. |

teste rápido e burn-in |

Qualquer falha neste teste faz com que o ikondiag comando gere o status normal do teste e mensagens de erro e, em seguida, termine com outra mensagem de erro. Você não pode continuar os testes porque todos os testes dependem da funcionalidade testada por este. |

Pcie |

Verifica a funcionalidade e a estabilidade das transferências em massa de dados PCIe. |

Volta repetidamente dados pseudo aleatórios gerados na CPU para o FPGA e depois de volta para a CPU. Os dados devolvidos são verificados na CPU. |

-i <n> número de repetições (padrão = 1 teste rápido, 10.000 burn-in) -j <n> tamanho da transferência individual em Mebibytes (padrão = 100 MiB). |

teste rápido e burn-in |

Este teste relata valores e compensações errôneas de dados na transferência de dados. Qualquer falha neste teste fará com que o comando ikondiag produza o status normal do teste e as mensagens de erro e, em seguida, termine com mais um erro. Você não pode continuar testando mais porque todos os testes dependem da funcionalidade testada por este teste. |

DIMM |

Verifica a funcionalidade de consulta do SPD e verifica se os DIMMs corretos estão instalados. |

Lê dados do dispositivo DOSP em módulos DIMM, relata conteúdo e verifica valores errôneos e verifica:

|

Nenhum. |

teste rápido e burn-in |

Se algum valor for inesperado, o teste relata valores errôneos e fornece valores e intervalos esperados. |

DRAMMemory |

Testa a funcionalidade de transferência de dados e a estabilidade dos dispositivos de memória DRAM conectados ao FPGA. |

|

-i <n> variar o número de iterações) padrão = 1 para teste rápido, 500 para burn-in) |

teste rápido e burn-in |

Este teste relata o número de erros durante a verificação. O número de erros é especificado como um número acumulado de erros por byte-lane e módulo DIMM. |

Testes e scripts de ethernet

Os testes e scripts da Ethernet testam portas C e tráfego entre portas A e B. O tráfego entre portas A e B é testado ao passar os dados nas portas F. Para as portas C, você precisa voltar atrás no tráfego enviado nas portas C. Você pode usar cabos físicos de loopback de cobre para esta finalidade. Para as portas F, você precisa voltar atrás no tráfego enviado nas portas F. Você pode usar cabos de loopback de cobre para esta finalidade. Inclua as portas F em uma VLAN. Você pode usar o script python PFAD_exec.py-t 1, bem como os testes abaixo. O script python PFAD_exec.py-t 1 verifica o tráfego L2 de ponta a ponta nas portas QSFP externas e verifica as estatísticas das interfaces no Junos OS e as estatísticas nas interfaces do software Packet Flow Diagnostics VM. Este teste falhará se a perda de tráfego for vista em alguma das interfaces. Há também uma disposição para testar todas as combinações de portas QSFP também.

Tabela 3 lista os nomes dos testes Ethernet e suas funções. Para obter informações sobre como instalar o script, veja ../topic-map/packet-flow-accelerator-diagnostics-software.html#id-installing-packet-flow-accelerator-diagnostics-software.

Nome do teste |

Descrição |

Detalhes |

Argumentos opcionais |

Conjuntos de testes |

Comportamento de falha |

|---|---|---|---|---|---|

QSFPEthernet |

Verifica a funcionalidade dos links Ethernet (QSFP). |

Gera, recebe e verifica se os quadros Ethernet estão na taxa de linha por meio do módulo FPGA. O conteúdo e os comprimentos dos pacotes consistem em dados pseudo-aleatórios. Durante a operação, as conexões QSFP são canalizadas para usar a Ethernet de 10 Gigabit com todos os 32 canais Ethernet operando em paralelo no modo full duplex. |

-i <n> número variado de iterações (padrão = 1.000 para teste rápido, 1e9 para burn-in) |

teste rápido e burn-in |

Se o número de pacotes enviados ou recebidos corretamente for verificado como não sendo igual, este teste é considerado uma falha e as discrepâncias entre essas quantidades são relatadas. Este teste falha se as conexões Ethernet externas não estiverem configuradas para loopback. |

QSFPI2C |

Verifique se há acesso aos quatro módulos QSFP localizados na frente do módulo QFX-PFA-4Q. |

Realiza leituras de registros nos módulos I2C e verifica se os resultados são os esperados. Para que este teste seja aprovado, a mídia QSFP deve ser inserida nas quatro portas do módulo QFX-PFA-4Q. Qualquer tipo de mídia externa pode ser usada (por exemplo, cabos DAC, loopback de cobre, módulos e módulos ópticos). |

Nenhum. |

teste rápido e burn-in |

Este teste falha se não conseguir detectar a presença de um módulo QSFP ou se os valores que ele lê de volta forem inesperados. |

Antes de executar os testes e o script da Ethernet com sucesso, você precisa executar as seguintes tarefas:

Loop externo de volta todas as conexões Ethernet (QSFP) no módulo QFX-PFA-4Q.

Para fazer loop de volta as interfaces QSFP no módulo QFX-PFA-4Q, conecte módulos de loopback de cobre nas quatro interfaces QSFP+ instaladas no módulo QFX-PFA-4Q.

Conecte módulos de loopback de cobre nas interfaces QSFP+ (portas 10 até a porta 13) instaladas no switch QFX5100-24Q-AA.

Canalize as portas de 10 a 13 no switch QFX5100-24Q-AA.

Emparelhe cada uma das 16 pistas ikonDiag usando os nomes equivalentes da interface do Junos OS com cada uma das interfaces correspondentes do Junos OS que foram canalizadas das portas de 10 a 13 no switch QFX5100-24Q-AA.

Nota:Cada VLAN deve ser independente de conter exatamente duas portas associadas — uma porta Ethernet de 10 Gigabits que é uma porta F e uma porta Ethernet de 10 Gigabits que é uma porta A.

Tabela 4 mostra os mapeamentos para os canais Ethernet de 10 Gigabit nas portas F do módulo QFX-PFA-4Q.

Tabela 4: Mapeamentos de canal Ethernet de 10 Gigabit nas portas F do módulo QFX-PFA-4Q Nomes de ikondiag

Descrição

JDFE_XE32_10G

xe-0/0/32

JDFE_XE33_10G

xe-0/0/33

JDFE_XE34_10G

xe-0/0/34

JDFE_XE35_10G

xe-0/0/35

JDFE_XE24_10G

xe-0/0/24

JDFE_XE25_10G

xe-0/0/25

JDFE_XE26_10G

xe-0/0/26

JDFE_XE27_10G

xe-0/0/27

JDFE_XE28_10G

xe-0/0/28

JDFE_XE29_10G

xe-0/0/29

JDFE_XE30_10G

xe-0/0/30

JDFE_XE31_10G

xe-0/0/31

JDFE_XE36_10G

xe-0/0/36

JDFE_XE37_10G

xe-0/0/37

JDFE_XE38_10G

xe-0/0/38

JDFE_XE39_10G

xe-0/0/39

Tabela 5 mostra os mapeamentos para os canais Ethernet de 10 Gigabit nas portas C do módulo QFX-PFA-4Q.

Tabela 5: Mapeamentos de canal Ethernet de 10 Gigabits nas portas C do módulo QFX-PFA-4Q Nomes de ikondiag

Descrição

JDFE_QSFP0_10G_PORT0

Porta QSFP nº 0 subcanal 10G 0

JDFE_QSFP0_10G_PORT1

Porta QSFP nº 0 subcanal 10G 1

JDFE_QSFP0_10G_PORT2

Porta QSFP nº 0 subcanal 10G 2

JDFE_QSFP0_10G_PORT3

Porta QSFP nº 0 subcanal 10G 3

JDFE_QSFP1_10G_PORT0

Porta QSFP nº 1 subcanal 10G 0

JDFE_QSFP1_10G_PORT1

Porta QSFP nº 1 subcanal 1 10G

JDFE_QSFP1_10G_PORT2

Porta QSFP nº 1 subcanal 10G 2

JDFE_QSFP1_10G_PORT3

Porta QSFP nº 1 subcanal 10G 3

JDFE_QSFP2_10G_PORT0

Porta QSFP nº 2 subcanal 10G 0

JDFE_QSFP2_10G_PORT1

Porta QSFP nº 2 subcanal 10G

JDFE_QSFP2_10G_PORT2

Porta QSFP nº 2 subcanal 10G 2

JDFE_QSFP2_10G_PORT3

Porta QSFP nº 2 subcanal 10G 3

JDFE_QSFP3_10G_PORT0

Porta QSFP nº 3 sub canal 10G 0

JDFE_QSFP3_10G_PORT1

Porta QSFP nº 3 subcanal 10G

JDFE_QSFP3_10G_PORT2

Porta QSFP nº 3 subcanal 10G 2

JDFE_QSFP3_10G_PORT3

Porta QSFP #3 subcanal 10G 3

Tabela 6 oferece conectividade exata entre as portas C e as portas A.

Tabela 6: Conectividade exata entre portas C e portas A Número da porta QSFP

Número do canal

Junos OS Interface

Porta QSFP nº 0

canal 0

xe-0/0/32

Porta QSFP nº 0

canal 1

xe-0/0/33

Porta QSFP nº 0

canal 2

xe-0/0/34

Porta QSFP nº 0

canal 3

xe-0/0/35

Porta QSFP nº 1

canal 0

xe-0/0/24

Porta QSFP nº 1

canal 1

xe-0/0/25

Porta QSFP nº 1

canal 2

xe-0/0/26

Porta QSFP nº 1

canal 3

xe-0/0/27

Porta QSFP 2

canal 0

xe-0/0/28

Porta QSFP 2

canal 1

xe-0/0/29

Porta QSFP 2

canal 2

xe-0/0/30

Porta QSFP 2

canal 3

xe-0/0/31

Porta QSFP nº 3

canal 0

xe-0/0/36

Porta QSFP nº 3

canal 1

xe-0/0/37

Porta QSFP nº 3

canal 2

xe-0/0/38

Porta QSFP nº 3

canal 3

xe-0/0/39

Adicione essas interfaces a uma VLAN.

Canalize portas de 10 a 13 usando o Junos CLI.

Configure portas de 10 a 13 no PIC 1 para operar como portas Ethernet de 10 Gigabit.

[edit chassis fpc 0 pic 1] user@switch# set port-range 10 13 channel-speed 10g

Analise sua configuração e emita o

commitcomando.[edit] user@switch# commit commit complete

Adicione as 16 interfaces canalizadas que você acabou de configurar para 16 VLANs.

Para adicionar as 16 interfaces canalizadas:

Crie 16 VLANs.

[edit vlans] user@switch# set v0_0 vlan-id 10 user@switch# set v0_1 vlan-id 11 user@switch# set v0_2 vlan-id 12 user@switch# set v0_3 vlan-id 13 user@switch# set v1_0 vlan-id 14 user@switch# set v1_1 vlan-id 15 user@switch# set v1_2 vlan-id 16 user@switch# set v1_3 vlan-id 17 user@switch# set v2_0 vlan-id 18 user@switch# set v2_1 vlan-id 19 user@switch# set v2_2 vlan-id 20 user@switch# set v2_3 vlan-id 21 user@switch# set v3_0 vlan-id 22 user@switch# set v3_1 vlan-id 23 user@switch# set v3_2 vlan-id 24 user@switch# set v3_3 vlan-id 25

Adicione as interfaces canalizadas às VLANs.

[edit interfaces] user@switch# set xe-0/0/24 unit 0 family ethernet-switching vlan members v0_0 user@switch# set xe-0/0/25 unit 0 family ethernet-switching vlan members v0_1 user@switch# set xe-0/0/10:0 unit 0 family ethernet-switching vlan members v0_0 user@switch# set xe-0/0/10:1 unit 0 family ethernet-switching vlan members v0_1 user@switch# set xe-0/0/10:2 unit 0 family ethernet-switching vlan members v0_2 user@switch# set xe-0/0/10:3 unit 0 family ethernet-switching vlan members v0_3 user@switch# set xe-0/0/11:0 unit 0 family ethernet-switching vlan members v1_0 user@switch# set xe-0/0/11:1 unit 0 family ethernet-switching vlan members v1_1 user@switch# set xe-0/0/11:2 unit 0 family ethernet-switching vlan members v1_2 user@switch# set xe-0/0/11:3 unit 0 family ethernet-switching vlan members v1_3 user@switch# set xe-0/0/12:0 unit 0 family ethernet-switching vlan members v2_0 user@switch# set xe-0/0/12:1 unit 0 family ethernet-switching vlan members v2_1 user@switch# set xe-0/0/12:2 unit 0 family ethernet-switching vlan members v2_2 user@switch# set xe-0/0/12:3 unit 0 family ethernet-switching vlan members v2_3 user@switch# set xe-0/0/13:0 unit 0 family ethernet-switching vlan members v3_0 user@switch# set xe-0/0/13:1 unit 0 family ethernet-switching vlan members v3_1 user@switch# set xe-0/0/13:2 unit 0 family ethernet-switching vlan members v3_2 user@switch# set xe-0/0/13:3 unit 0 family ethernet-switching vlan members v3_3

Analise sua configuração e emita o

commitcomando.[edit] user@switch# commit commit complete

Testes de estresse

Os testes de estresse exercem todos os E/S de alta velocidade em paralelo. Os testes de estresse exigem a mesma mídia externa que você usou para os testes de Ethernet.Tabela 7 lista o nome do teste e suas funções.

Nome do teste |

Descrição |

Detalhes |

Argumentos opcionais |

Conjuntos de testes |

Comportamento de falha |

|---|---|---|---|---|---|

Stress |

Exerce todos os E/S de alta velocidade em paralelo. |

Exerça todos os E/S de alta velocidade anexados ao FPGA em paralelo, incluindo:

Cada subsistema de teste é exercido de forma semelhante aos testes individuais descritos anteriormente. |

-i <n> número variado de iterações) padrão = 1 para teste rápido, 1.000 para burn-in) |

teste rápido e burn-in |

Se algum subsistema falhar, o teste será interrompido. O primeiro subsistema detectado com falha foi relatado. Nota:

Se vários subsistemas falharem, apenas o primeiro subsistema com falha é relatado. |

Testes de PTP

Você pode executar o PTP para hardware usado com PTP. Esses testes são úteis se você estiver criando aplicativos de tempo. Para executar os testes, você precisa conectar cabos subMiniature versão B (SMB), cabos de loopback Ethernet e cabos de loopback ToD para a porta serial de E/O, ToD e conectores Ethernet de 1 Gigabit. Você deve conectar os cabos de loopback SMB, Ethernet, ToD entre os conectores de saída e entrada de 10M e PPS. O cabo de loopback ToD é um cabo RJ45 padrão com o Pino 3 (Dados Tx) conectado ao Pino 6 (Rx Data). Além dos testes ptp, você pode executar scripts incluídos no software Packet Flow Accelerator Diagnostics para testar PTP. Veja Tabela 9 informações sobre os scripts do PTP. Os scripts de PTP exigem que você tenha uma imagem do Junos OS com o Enhanced Automation instalado no switch QFX5100-24Q-AA. Para obter informações sobre como instalar os scripts, veja ../topic-map/packet-flow-accelerator-diagnostics-software.html#id-installing-packet-flow-accelerator-diagnostics-software.

Tabela 8 lista os nomes dos testes de PTP e suas funções:

Nome do teste |

Descrição |

Detalhes |

Argumentos opcionais |

Conjuntos de testes |

Comportamento de falha |

|---|---|---|---|---|---|

PTP |

Verifica a funcionalidade de vários recursos de sincronização de tempo conectados ao FPGA do módulo QFX-PFA-4Q. |

Realiza vários testes na funcionalidade de sincronização de tempo do módulo QFX-BLUETOOTH-4Q. Os subestações cobertos por este teste incluem:

|

Nenhum. |

teste rápido e burn-in |

Uma falha em qualquer um dos subsistemas acima faz com que todo o teste falhe e gera um relatório no final do teste que indica o status de aprovação e reprovação dos sub-testes. |

Tabela 9 lista o nome do script e sua função. Este script não faz parte do ikondiag comando. Você pode executar este comando Junos OS.

Nome do script |

Descrição |

Detalhes |

Argumentos opcionais |

Conjuntos de testes |

Comportamento de falha |

|---|---|---|---|---|---|

./run_ptp_test |

Verifica a funcionalidade de vários recursos de sincronização de tempo conectados à FPGA do módulo QFX-PFA-4Q. |

Realiza vários testes na funcionalidade de sincronização de tempo do módulo QFX-PFA-4Q. Os sub-testes cobertos por este teste incluem:

|

Nenhum. |

Nenhum. Este teste deve ser executado manualmente. |

Uma falha em qualquer um dos subsistemas acima faz com que todo o teste falhe e gera um relatório no final do teste que indica o status de aprovação e reprovação dos sub-testes. |

Testes de LED de módulo QFX-PFA-4Q

Os testes de LED examinam os LEDs no módulo QFX-PFA-4Q.

Para executar o teste de LED, emita o ikon_led_toggle comando. O teste pode levar alguns segundos para começar porque o FPGA está sendo configurado. Quando você vê a mensagem Toggling LEDs. Send SIGINT (^C) to exit, o teste começa. Para encerrar o teste, digite Ctrl-C. Tabela 10 lista o nome do teste e sua função.

Nome do teste |

Descrição |

Detalhes |

Argumentos opcionais |

Conjuntos de testes |

Comportamento de falha |

|---|---|---|---|---|---|

ikon_led_toggle |

Pisca os LEDs no módulo QFX-PFA-4Q para inspeção visual. |

Os LEDs a seguir no módulo QFX-PFA-4Q passarão repetidamente pelos seguintes padrões: Nota:

Os LEDs AL e ST não estão incluídos neste teste.

|

Nenhum. |

Nenhum. Este teste deve ser executado manualmente. |

Os LEDs podem não piscar. |

Serviços de diagnóstico do Packet Flow Accelerator

Além dos testes de software Packet Flow Accelerator Diagnostic, existem utilitários incluídos no software Packet Flow Accelerator Diagnostics que você pode usar para diagnosticar mais problemas no módulo QFX-PFA-4Q.

Antes de executar os serviços públicos, você precisa se conectar ao console do VM convidado. Para obter mais informações sobre como acessar o VM convidado, veja ../topic-map/packet-flow-accelerator-diagnostics-software.html#id-installing-packet-flow-accelerator-diagnostics-software.

Tabela 11 lista o nome da utilidade e sua função.

Nome do teste |

Descrições |

Detalhes |

Saída e comportamento esperados |

|---|---|---|---|

maxtop |

Relata o status do FPGA. |

Exibe informações sobre o status configurado atualmente do módulo FPGA e se o módulo está em operação. Verificações para garantir que as operações básicas de driver e link FPGA PCI Express estejam funcionando corretamente. Se este utilitário sair com(s) erro(s), é muito improvável que outras operações de FPGA funcionem. |

A saída deve ser semelhante à mostrada abaixo. Se essa saída não for mostrada, pode haver uma falha crítica no ambiente do software de diagnóstico ou o link PCI Express para o FPGA não for funcional.

|

ikon_snake |

Permite a conectividade entre todos os canais Ethernet de 10 Gigabit. |

Conecta o canal Rx de todos os canais Ethernet de 32 x 10 Gigabit no módulo FPGA (interfaces QSFP) ao canal Tx da respectiva conexão vizinha. Isso permite que todos os 32 canais sejam testados usando apenas um gerador de pacotes externos de interface Ethernet de 10 Gigabits, módulos de loopback de cobre e um cabo de separação QSFP <-> 4xSFP. |

Após a emissão deste teste, todos os dados da Ethernet serão encaminhados após a exibição da mensagem Nota:

Durante o tempo antes da impressão da mensagem de operação, o módulo FPGA pode estar em processo de configuração, para que nenhum dados seja encaminhado. Pressionar "entrar" sairá do utilitário. Após o término do teste, os dados do pacote continuam a ser encaminhados até que outro utilitário ou teste da Ethernet seja executado. |

ikon_eth_util tudo --digitalloopback |

Permite o loopback digital em todas as interfaces Ethernet de 10 Gigabits na conectividade "cobra" entre todos os canais Ethernet de módulo QFX-PFA-4Q de 10 Gigabits. |

Conecta o lado Rx de todos os canais Ethernet de 32x 10 Gigabit no módulo FPGA (QSFP) ao lado Tx do mesmo canal. |

Após a emissão deste teste, todos os dados da Ethernet serão encaminhados conforme descrito após a exibição da mensagem Nota:

Antes que a mensagem de operação seja exibida, o módulo FPGA pode estar em processo de configuração, e nenhum dados será encaminhado. Pressionar Enter sai do utilitário. Após o término do teste, os dados do pacote continuam a ser encaminhados até que outro utilitário ou teste da Ethernet seja executado. |

ikon_eth_util |

Permite que os dados passem pelas portas QSFP do módulo QFX-PFA-4Q. |

Permite que os dados passem pelas portas QSFP do módulo QFX-PFA-4Q no módulo QFX-PFA-4Q. Nota:

Como todas as portas QSFP são canalizadas para Ethernet de 10 Gigabits, você deve usar cabos de separação SFP ao conectar mídia externa. |

Após a emissão deste teste, todos os dados da Ethernet são encaminhados conforme descrito após a mensagem " executando a chave de retorno da imprensa para a saída " ser exibida. Nota:

Antes que a mensagem de operação seja exibida, o módulo FPGA pode estar em processo de configuração, e nenhum dados será encaminhado. Pressionar "entrar" sairá do utilitário. Após o término do teste, os dados do pacote continuarão a ser encaminhados até que outro utilitário ou teste da Ethernet seja executado. |

maxnet -v link show |

Despejos de estatísticas de pacotes FPGA. |

Exibe estatísticas sobre pacotes enviados e recebidos em todos os links (QSFP) dos núcleos DE IP MAC e PHY no FPGA. Usar a opção "v" oferece saída verbosa. Aqui estão alguns itens importantes a observar:

|

A saída de amostra para um único link Ethernet de 10 Gigabits é a seguinte: MaxTop Tool 2015.1

Found 1 card(s) running MaxelerOS 2015.1

Card 0: QFX-PFA-4Q (P/N: 241124) S/N: 96362301684266423 Mem: 24GB

Load average: 0.00, 0.00, 0.00

DFE %BUSY TEMP MAXFILE PID USER TIME COMMAND

0 0.0% - 2fcf249cc7... - - - -

|

host2mem I <filename> -o <filename> -t <DDR | QDR0 | QDRPARITY0 | QDR1 | QDRPARITY1> |

Escreve e lê dados arbitrários da QDR SRAM ou DRAM. |

Opera transmitindo o conteúdo de um arquivo binário para um dos recursos de memória no módulo QFX-PFA-4Q através do FPGA e, em seguida, transmite os mesmos dados de volta da memória para outro arquivo. Nota:

Você não pode apenas ler dados de volta da RAM porque o conteúdo não está preservado entre a execução de vários testes. |

Os relatórios passaram ou falharam dependendo se os dados devolvidos correspondem aos dados de entrada. |

Tabela 12 lista os argumentos da linha de comando para o utilitário host2mem.

Argumento |

Descrição |

|---|---|

ajuda | -h |

Imprima o uso e a saída. |

Arquivo de <input> |

Arquivo de dados de entrada. |

arquivo de <output> |

Arquivo de dados de saída. |

teste | -t <esta nome> |

Testar recursos. Veja Tabela 13 informações sobre os recursos. |

verboso | -v |

Habilite o modo verbose. |

O formato do arquivo para arquivos de entrada e saída é idêntico. Os dados são embalados consecutivamente como palavras com base na largura especificada na tabela de modo de teste abaixo. O tamanho de um arquivo de entrada pode ser menor, mas não deve exceder o tamanho total do recurso que está sendo testado. O tamanho do arquivo de saída é o mesmo que o arquivo de entrada e, desde que não haja erros, tenha o mesmo conteúdo.

Modo de teste |

Recurso |

Largura de palavra |

Tamanho dos dados de teste |

|---|---|---|---|

DDR |

DDR SDRAM |

192 B |

24 GB |

QDR0 |

Dados QDR0 |

16 B |

32 MB |

QDRPARITY0 |

Bits de paridade QDR0 |

2 B |

4 MB |

QDR1 |

Dados do QDR1 |

16 B |

32 MB |

QDRPARITY1 |

Bits de paridade QDR1 |

2 B |

4 MB |

A memória dinâmica de acesso aleatório (DRAM) no módulo QFX-PFA-4Q contém três módulos de memória dupla em linha (DIMM3, DIMM4, DIMM6), e cada palavra de dados é dividida entre os três DIMMs.Tabela 14 lista a alocação de Bytes para DIMMs.

0 |

DIMM3 |

63 |

64 |

DIMM4 |

127 |

128 |

DIMM6 |

191 |

Saída de amostra para software de diagnósticos packet accelerator

Esta seção fornece alguma saída de amostra para testes base, testes Ethernet, testes PTP e utilitários.

ikondiag -t FPGABasic

[2015-05-07 03:00:17][BEGIN TEST - FPGABasic] [2015-05-07 03:00:17][END TEST FPGABasic RESULT PASSED]

ikondiag -t DIMM

[2015-05-07 03:01:09][BEGIN TEST - DIMM] [2015-05-07 03:01:09][END TEST DIMM RESULT PASSED]

ikondiag -t QSFPEthernet

[2015-05-07 03:02:33][BEGIN TEST - QSFPEthernet] *********************************************** Test Failed: QSFP0_10G_PORT0: FAIL - packets received = 0/1000 QSFP0_10G_PORT1: FAIL - packets received = 0/1000 QSFP0_10G_PORT2: FAIL - packets received = 0/1000 QSFP0_10G_PORT3: FAIL - packets received = 0/1000 QSFP1_10G_PORT0: FAIL - packets received = 0/1000 QSFP1_10G_PORT1: FAIL - packets received = 0/1000 QSFP1_10G_PORT2: FAIL - packets received = 0/1000 QSFP1_10G_PORT3: FAIL - packets received = 0/1000 QSFP2_10G_PORT0: FAIL - packets received = 0/1000 QSFP2_10G_PORT1: FAIL - packets received = 0/1000 QSFP2_10G_PORT2: FAIL - packets received = 0/1000 QSFP2_10G_PORT3: FAIL - packets received = 0/1000 QSFP3_10G_PORT0: FAIL - packets received = 0/1000 QSFP3_10G_PORT1: FAIL - packets received = 0/1000 QSFP3_10G_PORT2: FAIL - packets received = 0/1000 QSFP3_10G_PORT3: FAIL - packets received = 0/1000 QSFP4_10G_PORT0: PASS - packets received = 1000/1000 QSFP4_10G_PORT1: PASS - packets received = 1000/1000 QSFP4_10G_PORT2: PASS - packets received = 1000/1000 QSFP4_10G_PORT3: PASS - packets received = 1000/1000 QSFP5_10G_PORT0: PASS - packets received = 1000/1000 QSFP5_10G_PORT1: PASS - packets received = 1000/1000 QSFP5_10G_PORT2: PASS - packets received = 1000/1000 QSFP5_10G_PORT3: PASS - packets received = 1000/1000 QSFP6_10G_PORT0: PASS - packets received = 1000/1000 QSFP6_10G_PORT1: PASS - packets received = 1000/1000 QSFP6_10G_PORT2: PASS - packets received = 1000/1000 QSFP6_10G_PORT3: PASS - packets received = 1000/1000 QSFP7_10G_PORT0: PASS - packets received = 1000/1000 QSFP7_10G_PORT1: PASS - packets received = 1000/1000 QSFP7_10G_PORT2: PASS - packets received = 1000/1000 QSFP7_10G_PORT3: PASS - packets received = 1000/1000 *********************************************** [2015-05-07 03:02:41][END TEST QSFPEthernet RESULT PASSED]

ikondiag -t DRAMMemory -i 3

[2015-05-07 03:03:37][BEGIN TEST - DRAMMemory] [2015-05-07 03:04:21][END TEST DRAMMemory RESULT PASSED]

ikondiag -t QDRMemory -p -i 3

[2015-05-07 03:10:38][BEGIN TEST - QDRMemory] [2015-05-07 03:10:45][END TEST QDRMemory RESULT PASSED]

ikondiag -t Estresse -p -i 10

[2015-05-07 03:11:24][BEGIN TEST - Stress] *********************************************** Test Failed: QSFP0_10G_PORT0: PASS - packets received = 650000/650000 QSFP0_10G_PORT1: PASS - packets received = 650000/650000 QSFP0_10G_PORT2: PASS - packets received = 650000/650000 QSFP0_10G_PORT3: PASS - packets received = 650000/650000 QSFP1_10G_PORT0: PASS - packets received = 650000/650000 QSFP1_10G_PORT1: PASS - packets received = 650000/650000 QSFP1_10G_PORT2: PASS - packets received = 650000/650000 QSFP1_10G_PORT3: PASS - packets received = 650000/650000 QSFP2_10G_PORT0: PASS - packets received = 650000/650000 QSFP2_10G_PORT1: PASS - packets received = 650000/650000 QSFP2_10G_PORT2: PASS - packets received = 650000/650000 QSFP2_10G_PORT3: PASS - packets received = 650000/650000 QSFP3_10G_PORT0: PASS - packets received = 650000/650000 QSFP3_10G_PORT1: PASS - packets received = 650000/650000 QSFP3_10G_PORT2: PASS - packets received = 650000/650000 QSFP3_10G_PORT3: PASS - packets received = 650000/650000 QSFP4_10G_PORT0: PASS - packets received = 650000/650000 QSFP4_10G_PORT1: PASS - packets received = 650000/650000 QSFP4_10G_PORT2: PASS - packets received = 650000/650000 QSFP4_10G_PORT3: PASS - packets received = 650000/650000 QSFP5_10G_PORT0: PASS - packets received = 650000/650000 QSFP5_10G_PORT1: PASS - packets received = 650000/650000 QSFP5_10G_PORT2: PASS - packets received = 650000/650000 QSFP5_10G_PORT3: PASS - packets received = 650000/650000 QSFP6_10G_PORT0: PASS - packets received = 650000/650000 QSFP6_10G_PORT1: PASS - packets received = 650000/650000 QSFP6_10G_PORT2: PASS - packets received = 650000/650000 QSFP6_10G_PORT3: PASS - packets received = 650000/650000 QSFP7_10G_PORT0: PASS - packets received = 650000/650000 QSFP7_10G_PORT1: PASS - packets received = 650000/650000 QSFP7_10G_PORT2: PASS - packets received = 650000/650000 QSFP7_10G_PORT3: PASS - packets received = 650000/650000 ***********************************************

ikondiag -t PTP

[2015-05-07 03:12:20][BEGIN TEST - PTP] ************************************************************************* PTP PHY interrupt: PASS 1G Ethernet PHY packet loopback test: PASS PTP clock generation/check: PASS UART (ToD) loopback: PASS ************************************************************************* [2015-05-07 03:13:30][END TEST PTP RESULT PASS]

ikondiag -t Aplicativo -i 2

iterations = 2 [2015-05-07 03:14:11][BEGIN TEST - Application Test] [2015-05-07 03:17:33][END TEST Application Test RESULT PASSED]

maxtop

MaxTop Tool 2015.1 Found 1 card(s) running MaxelerOS 2015.1 Card 0: (P/N: 241124) S/N: 96362301684266423 Mem: 24GB Load average: 0.00, 0.00, 0.00 DFE %BUSY TEMP MAXFILE PID USER TIME COMMAND 0 0.0% - 7e2198e5c0... - - - -

ikon_eth_util , tudo-pass-through

Ikon Ethernet Pass Through Utility setting portConnect_QSFP4_10G_PORT0_QSFP0_10G_PORT0 to 1 setting portConnect_QSFP4_10G_PORT1_QSFP0_10G_PORT1 to 1 setting portConnect_QSFP4_10G_PORT2_QSFP0_10G_PORT2 to 1 setting portConnect_QSFP4_10G_PORT3_QSFP0_10G_PORT3 to 1 setting portConnect_QSFP1_10G_PORT0_QSFP5_10G_PORT0 to 1 setting portConnect_QSFP1_10G_PORT1_QSFP5_10G_PORT1 to 1 setting portConnect_QSFP1_10G_PORT2_QSFP5_10G_PORT2 to 1 setting portConnect_QSFP1_10G_PORT3_QSFP5_10G_PORT3 to 1 setting portConnect_QSFP2_10G_PORT0_QSFP6_10G_PORT0 to 1 setting portConnect_QSFP2_10G_PORT1_QSFP6_10G_PORT1 to 1 setting portConnect_QSFP2_10G_PORT2_QSFP6_10G_PORT2 to 1 setting portConnect_QSFP2_10G_PORT3_QSFP6_10G_PORT3 to 1 setting portConnect_QSFP3_10G_PORT0_QSFP7_10G_PORT0 to 1 setting portConnect_QSFP3_10G_PORT1_QSFP7_10G_PORT1 to 1 setting portConnect_QSFP3_10G_PORT2_QSFP7_10G_PORT2 to 1 setting portConnect_QSFP3_10G_PORT3_QSFP7_10G_PORT3 to 1 running press return key to exit